Digitalni elektronski sistemi

UNI, 4. semester (2-0-2)

Vsebina

Postopek zasnove digitalnih sistemov in tiskanih vezij. Model vezja in realno vezje. Programirljive naprave FPGA in sistemi na integriranem vezju. Načrtovanje vezij v strojno-opisnem jeziku: signali, izrazi, opis zgradbe in obnašanja, sekvenčna vezja in testne strukture. Pravila za avtomatsko sintezo logike. Načrtovanje in optimizacija digitalnih vezij na ravni registrov (RTL). Ocenjevanje digitalnih sistemov z vidika zmogljivosti, velikosti, cene, porabe moči in razvojnega časa. Primer zasnove preprostega digitalnega elektronskega sistema: od algoritma do izvedbe v ciljni tehnologiji. Mikroprocesorji v digitalnih sistemih, zgradba in delovanje procesorja RISC V. Digitalni vmesniki.

| Predavanja | Projekt |

|---|---|

|

Laboratorijske vaje

Laboratorijske vaje začnemo prvi teden v marcu 2025.

Spletna učilnica za študijsko leto 2024/25: ucilnica-fe.

- Kombinacijska vezja

- Števci

- Utripanje LED (stevec.zip)

- Digitalno sito (TestFIR.vhd)

- Shema in tiskano vezje

- Generator

- Frekvenca (gensig.zip)

- Projekt 1 (sint25.zip)

Literatura

- A. Trost: Osnove modeliranja digitalnega vezja v strojno-opisnem jeziku, FE, 2020

- Harris & Harris: Digital Design and Computer Architecture, Morgan Kaufmann, 2007

- A. Trost: "Načrtovanje digitalnih vezij v jeziku VHDL", založba FE/FRI, 2011

- M. M. Mano: "Logic and Computer Design Fundamentals", Prentice Hall, 2007

- B.J. LaMeres: Quick Start Guide to VHDL, Springer, 2019

- E. Borin, An Introduction to Assembly Programming with RISC-V, Institute of Computing, Brasil, 2021

- DES 2017

Gradivo za predavanja

* gradivo ima na koncu povzetek vprašanj za utrjevanje snovi.

Literatura

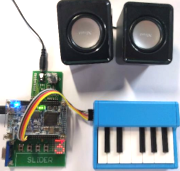

Projekt: elektronske orgle

|  |

Laboratorijske vaje

Urnik laboratorijskih vaj: sreda 15h (LEV, M-Ro), četrtek 11h (LEV, Ru-Z), četrtek 16h (LRNV, A-K)

Povezava za prenos datotek: file_sharing

- Vhodno-izhodni vmesnik (avdio_vmes.zip)

- Kombinacijska vezja

- PWM (sistemDES3.qar)

- Sekvenčno digitalno sito (TestFIR.vhd)

- Oscilator s pulzno-širinskim modulatorjem (sistem.zip)

- Generator tonov (generator.zip)

- Generator sinusnih tonov (rom.vhd), PS/2 vmesnik (testPS2.vhd), VGA (DE0_VGA.zip)

- Generator z ovojnico, Vmesnik z dekodirnikom, Grafika s slikami (grafikaTB.vhd)

- Preizkus generatorja, sistemPS.zip, Preizkus grafike

- DES 2016

Gradivo za predavanja

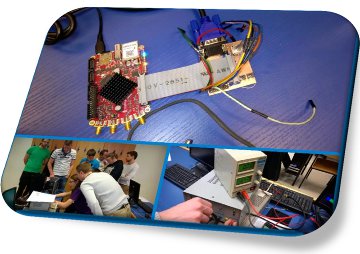

Projekt: Red Pitaya digitalni osciloskop (pdf)

VabiloVabljeni na predavanje v sredo 26.4. ob 17h-18h v P11, ki ga organiziramo s podjetjem Avnet Silica. Podjetje se ukvarja z distribucijo elektronskih komponent in svetovanjem razvojnim inženirjem. Predstavljene bodo aktualne tehnologije in novosti s področja FPGA, razvojna orodja in znanja, ki se pričakujejo od današnjih razvojnikov. |

|

Laboratorijske vaje

Drugo poročilo iz laboratorijskih vaj pripravite do 12.6. in oddajte v obliki pdf po elektronski pošti. Poročilo naj bo v obliki kratkega opisa komponente IP (IPosc, IPgraf oz. IPvmesnik), ki obsega največ 2 strani. Poleg poročila oddajte tudi arhivsko datoteko (*.zip) z vašo komponento (samo arhiv komponente, ne celega projekta!). Opis komponente IP naj vsebuje:

- predstavitev komponente, na kratko opišite kaj dela,

- blokovna z zunanjimi signali in tabela z opisom vsakega signala: ime, smer, podatkovni tip in kratka razlaga,

- opis glavnih sestavnih delov (vključene komponente, procesi),

- kratka predstavitev delovanja in

- povzetek rezultatov sinteze v izbrano vezje FPGA

- Shema vezja (Navodila za Eagle)

- Vhodno-izhodni vmesnik

- Kombinacijska vezja (Navodila za Vivado)

- Sekvenčno digitalno sito (TestFIR.vhd)

| Vmesnik | Grafika | Logika |

|---|---|---|

|

- DES 2015

Gradivo za predavanja

Projekt: Red Pitaya logični analizator (pdf)

Poročilo

|

|

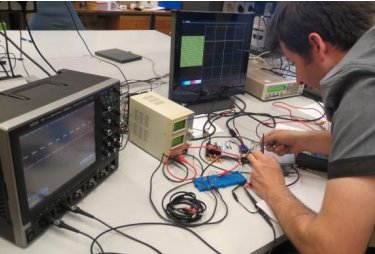

Laboratorijske vaje

Laboratorijske vaje se začnejo 8.3., o razdelitvi v skupine se bomo dogovorili na predavanjih.

Predlog: A-Ka četrtek 16h, Kl-Pa četrtek 18h, Pe-Ž torek 16h.

- Shema vezja (Navodila za Eagle)

- Tiskano vezje

- Kombinacijska vezja (Navodila za Vivado)

- Sekvenčno vezje in arhitektura 1 (pdf, xc9572xl-tq100.lbr)

- serijski vmesnik (TestSpr.vhd), VGA (VGAtest.vhd, vga.xdc) in arhitektura 2 (pdf)

- Grafika 2 (pdf, slika.vhd) in arhitektura 3 (pdf, pravila.zip)

- Grafika 3 (pdf, crom.vhd, TB_VGAtest.vhd), Vmesnik 2 (pdf, TBzajem.vhd)

- Grafika 4 (pdf), Vmesnik 3 (pdf)

- Grafika 5 (pdf), Vmesnik 4 (pdf) in arhitektura 4 (pdf)

- Kodiranje VGA (pdf, VGAkod.vhd), Sistem VGA (pdf, RedPitayaVGA.zip)

- Testni projekt: RedPitaya.zip

(c) LNIV 2022