Navodila za SHDL (V.38)

SHDL | Sintaksa | Prevajanje in analiza

SHDL (Small Hardware Description Language) je poenostavljen jezik za modeliranje digitalnih vezij, po zgledu standardnega strojno-opisnega jezika VHDL. Model vezja opišemo z eno- ali večbitnimi signali, ki imajo celoštevilske vrednosti, prireditvenimi izrazi in pogojnimi stavki. Spletno orodje SHDL omogoča izdelavo, analizo in simulacijo modela vezja v SHDL ter avtomatsko pretvorbo v VHDL.

Modeliranje in simulacija v treh korakih

| 1. Nov model | 2. Opis in prevajanje | 3. Simulacija vezja |

|---|---|---|

|  |  |

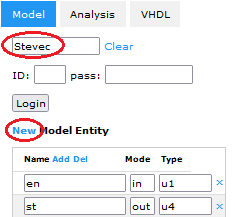

1. Nov model

Izdelavo novega vezja začnemo v zavihku Model , kjer v okencu

določimo ime vezja in v tabeli definiramo signale.

V tabeli signalov dodajamo nove vrstice z Add, Del pa izbriše zadnjo vrstico.

Signalom določimo ime, vrsto in podatkovni tip.

- Signali vrste in so vhodi, out so izhodi, za notranje signale pa pustimo prazno polje.

- Tip določa črka u (unsigned) ali s (signed) in število bitov, ki je med 1 in 64.

- V vrstici tabele lahko deklariramo več signalov enake vrste tako, da vnesemo imena ločena z vejico.

- Signale naštevnega tipa ne moremo deklarirati v tabeli.

Primer: u1 - enobitni, u4 - 4-bitni nepredznačen in s8 je 8-bitni predznačen signal.

Klik na New naredi opis entitete vezja in deklaracijo signalov.

Namig

Nov model vezja lahko naredimo tudi brez tega koraka, vendar izpolnjeno tabelo potrebujemo za simulacijo.

Ko vezje prevedemo, v tabeli Wave Ports & Signals določamo signale prikazane na simulacijskem grafu.

Pred izdelavo novega modela počistimo SHDL in vsebino tabele s klikom na Clear.

2. Opis in prevajanje

Vezje opišemo s prireditvenimi in pogojnimi stavki v poenostavljeni sintaksi SHDL. Model vezja sestavlja: ime entitete, deklaracija signalov in blok stavkov med begin in end. Stavki se izvajajo paralelno (sočasno), ker predstavljajo opis delov vezja.

- Blok stavkov je zaporedje stavkov, ki so vsak v svoji vrstici ali pa ločeni s podpičjem.

- Prireditveni stavki z operatorjem

=se izvedejo takoj (kombinacijsko), z operatorjem<=pa ob fronti ure (sekvenčno). - Pogojni stavek v katerem je en sam stavek zapišemo kompaktno: "if (pogoj) stavek",

če mu sledi blok več stavkov pa v obliki: "if pogoj then blok stavkov end".

Pogojni stavek pozna tudi else in elsif za zaporedne pogoje, kot v jeziku VHDL. - Znotraj bloka lahko le enkrat priredimo vrednost posameznemu signalu!

- Vrstni red prireditev različnim signalom znoraj bloka ni pomemben.

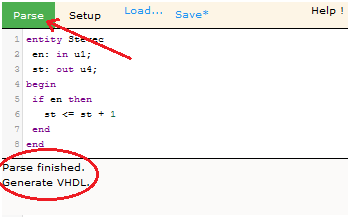

Primer: model 4-bitnega števca z omogočanjem štetja (en)

entity stevec

| Namig: Signal za uro (clk) NE deklariramo, ker je v jeziku SHDL privzet ob uporabi sekvenčnih prireditev. Podobno velja tudi za asinhroni reset (rst), če smo v nastavitvah izbrali asinhrono resetiranje. |

Prevajanje modela izvedemo s klikom na gumb Parse . Nastavitve prevajalnika odpremo na gumbu Setup in zapremo s ponovnim klikom na ta gumb.

Prevajalnik bo pod opisom vezja javil uspešen zaključek (Parse finished.) ali pa sporočil napako. Sporočilo o napaki vsebuje kratek opis in mesto. Primer: Napaka v 1:8: Pričakujem ')'! sporoča, da smo v prvi vrstici na 8 mestu verjetno pozabili zaklepaj.Ko model prevedemo brez napak, dobimo v zavihku Analysis tabelo Resources s seznamom zaznanih gradnikov vezja. Zavihek VHDL prikaže opis modela vezja, ki je pretvorjen v jezik VHDL. Klik na copy uporabimo za enostaven prenos opisa v odložišče in nato v programsko opremo za prevajanje logike v jeziku VHDL.

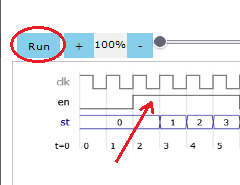

3. Simulacija vezja

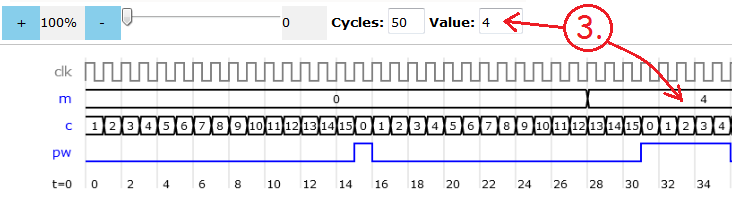

Simulacijo izvedemo tako, da v oknu s signali nastavimo vrednosti vhodnih signalov in izvedemo Run .

- Enobitne vhode spreminjamo z levim klikom na posamezen cikel ali potegom čez več ciklov.

- Vektorski vhodi dobijo ob kliku vrednost, ki je vpisana v okence Value.

Če je obkljukan autoinc, se bo vrednost ob vsakem kliku povečala za 1. - Vse cikle nekega signala nastavimo tako, da kliknemo na ime signala in potrdimo nastavitev.

- Z desnim klikom na signal preklapljamo med desetiškim, dvojiškim in analognim prikazom.

Namig

Število simulacijskih ciklov določimo v okencu Cycles. Ob ponovnem kliku na Run, se simulacija sekvenčnega vezja nadaljuje od zadnjega stanja. Simulacijo od začetnega (reset) stanja izvedemo tako, da najprej ponovno prevedemo vezje.

Primer: simulacija pulzno-širinskega modulatorja. Vhod m nastavimo tako, da vpišemo vrednost v okence Value, nato pa spremenimo vrednosti grafa s klikom na ustrezne cikle.

entity pwm

|

|

Shranjevanje modelov vezja

Save shrani model vezja v obliki tekstovne datoteke s končnico .shdl. Spletni brskalnik bo shranil datoteko v privzeto mapo (downloads), od koder jo v operacijskem sistemu prenesemo v svojo mapo. Če imamo v nastavitvah obkljukan save waveform, se bodo poleg modela shranili tudi simulacijski vhodni signali.

Load... uporabimo za nalaganje modela vezja iz lokalnega računalnika v spletni brskalnik.

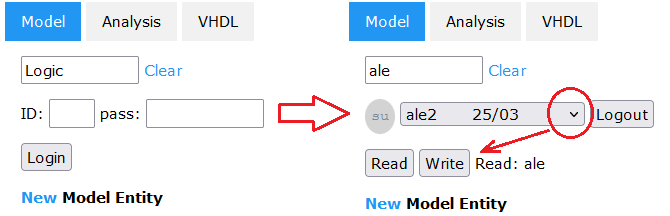

Orodje SHDL omogoča tudi shranjevanje na spletni strežnik, ki zahteva prijavo z geslom. Podatke za prijavo vam posreduje predavatelj predmeta, kjer uporabljamo SHDL. Po vnosu identitete (ID) in gesla (pass) se pojavi seznam v strežniku shranjenih datotek. Iz seznama izberemo model vezja in ga z gumbom Read prenesemo v spletno orodje, za shranjevanje na strežnik pa uporabimo Write . Model se shrani pod imenom vezja (entitete), zato pazimo, da ima novo vezje drugačno ime, sicer se podatki prepišejo!