Fakulteta za elektrotehniko -

Tržaška 25 - 1000 Ljubljana - Slovenija

Laboratorij za načrtovanje integriranih vezij

Tel: +386 1 4768 351

Predmeti

1. stopnja

- Digitalni elektronski sistemi (UNI)

- Programirljivi digitalni sistemi (VS)

- Modul B: IV / NDES (VS)

2. stopnja

3. stopnja

Dodiplomski (stari)

Podiplomski (stari)

Projekti in diplome

Digitalni elektronski sistemi UNI

4. semester (2-0-2)

Opis | DES 2015 | DES 2014 | DES 2013 | DES 2012 | DES 2011 | DES 2010 | VHDL osnove | Grafični TestBench | Spartan-3 modul

Gradivo za predavanja

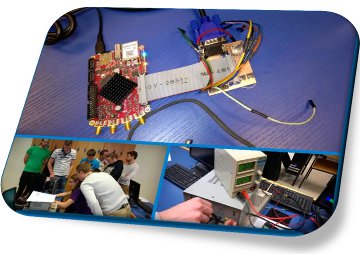

Projekt: Red Pitaya digitalni osciloskop (pdf)

VabiloVabljeni na predavanje v sredo 26.4. ob 17h-18h v P11, ki ga organiziramo s podjetjem Avnet Silica. Podjetje se ukvarja z distribucijo elektronskih komponent in svetovanjem razvojnim inženirjem. Predstavljene bodo aktualne tehnologije in novosti s področja FPGA, razvojna orodja in znanja, ki se pričakujejo od današnjih razvojnikov. |

|

Laboratorijske vaje

Drugo poročilo iz laboratorijskih vaj pripravite do 12.6. in oddajte v obliki pdf po elektronski pošti. Poročilo naj bo v obliki kratkega opisa komponente IP (IPosc, IPgraf oz. IPvmesnik), ki obsega največ 2 strani. Poleg poročila oddajte tudi arhivsko datoteko (*.zip) z vašo komponento (samo arhiv komponente, ne celega projekta!). Opis komponente IP naj vsebuje:

- predstavitev komponente, na kratko opišite kaj dela,

- blokovna z zunanjimi signali in tabela z opisom vsakega signala: ime, smer, podatkovni tip in kratka razlaga,

- opis glavnih sestavnih delov (vključene komponente, procesi),

- kratka predstavitev delovanja in

- povzetek rezultatov sinteze v izbrano vezje FPGA

- Shema vezja (Navodila za Eagle)

- Vhodno-izhodni vmesnik

- Kombinacijska vezja (Navodila za Vivado)

- Sekvenčno digitalno sito (TestFIR.vhd)

| Vmesnik | Grafika | Logika |

|---|---|---|

|