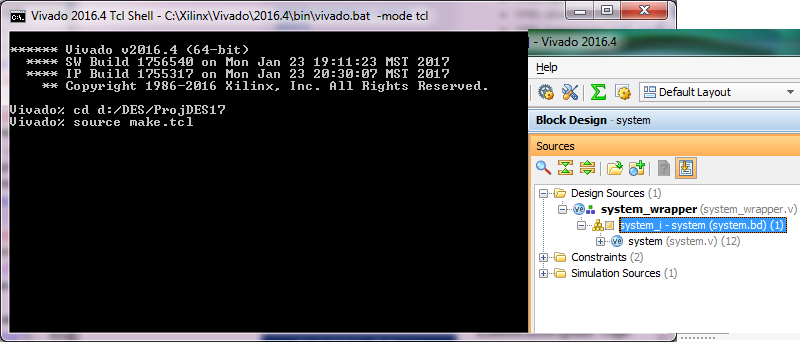

Naredi novo mapo za tesni projekt in odpakiraj datoteke iz arhiva ProjDES17.zip. V arhivu so komponente in nastavitve projekta v skripti, zato bomo tokrat odprli program Vivado v skriptnem načinu: Xilinx Design Tools > Vivado 2016.4 > Vivado 2016.4 Tcl Shell. Najprej se prestavi v ustrezno mapo, nato pa izvedi skripto: source make.tcl

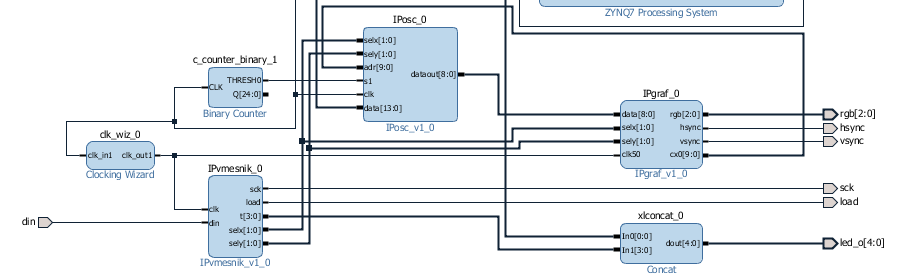

Skripta ustvari nov projekt v podmapi RPVGA in po uspešnem zaključku odpre program Vivado v grafičnem načinu. Zgradbo vezja vidimo, če odpremo blokovno shemo (Open Block Design). Za nas je zanimiv spodnji del sheme, kjer so povezane komponente osciloskopa. Komponenta IPosc je vezana na uro adc_clk frekvence 125 MHz, IPvmesnik in IPgraf pa imata uro frekvence 50 MHz, ki jo dobimo iz komponente Clocking Wizard. V vezju je še 25 bitni števec Binary Counter iz katerega dobimo periodičen signal (s1) za proženje zajema podatkov v komponenti IPosc. Izhodne LED uporabimo za osnovno indikacijo delovanja vezja: na eno LED je vezan periodičen signal iz procesorja, na naslednje pa izhodi tipk (t) iz vmesnika IPvmesnik.

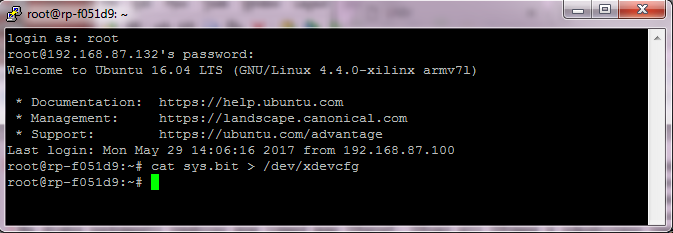

Projekt prevedemo z Run Implementation in Generate Bitstream. Izhodna datoteka z imenom system_wrapper.bit se nahaja v mapi: ProjDES17\RPVGA\RPVGA.runs\impl_1.

Zamenjaj eno izmed komponent IP, ki se nahajajo v podmapi ProjDES17\cores z lastno komponento. Na disku nadomesti vsebino ene izmed map IPgraf, IPosc ali IPvmes z odpakirano vsebino arhivske datoteke, ki si jo naredil pri zadnji vaji. Če ima komponenta enako ime in popolnoma enake zunanje signale, je najlažje kar na novo narediti projekt z ukazom source make.tcl

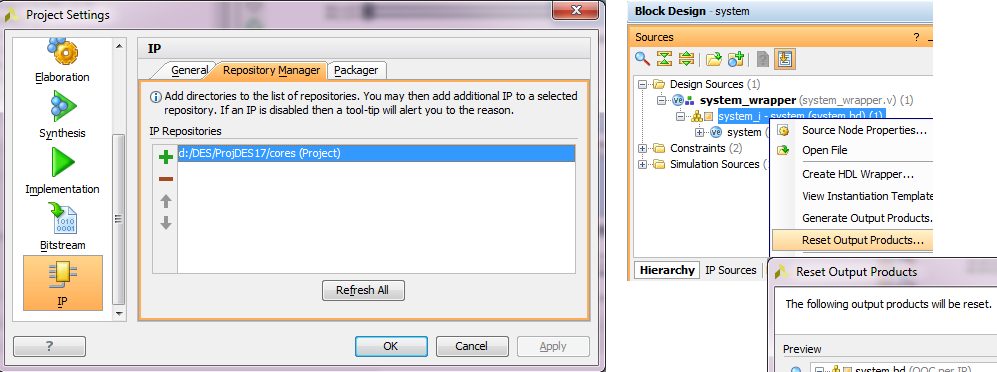

Če imamo drugačno koponento je potrebno najprej v programu Vivado osvežiti seznam komponent IP v projektu: Project Settings, klikni na IP, izberi zavihek Repositora Manager in klikni Refresh All. Program bo nato zahteval poročilo statusa (Tools > Report IP Status) in posodobitev spremenjene komponente, ki jo dosežemo s klikom Upgrade Selected.

Pred prevajanjem je dobro, da sami resetiramo vsebino vključenih datotek. V oknu Sources izberi zavihek Hierarchy in z desnim klikom na system.bd izberi Reset Output Products ter potrdi s gumbom Reset, nato pa ponovno prevedi projekt.