Laboratorij za načrtovanje integriranih vezij - Fakulteta za elektrotehniko, Ljubljana

Razvojna plošča S3A

Opis razvojne plošče S3A

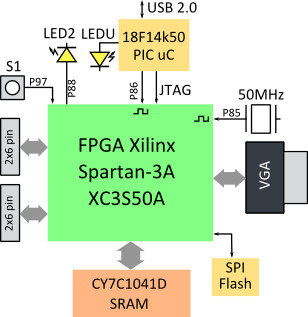

Vezje razvojne plošče vsebuje FPGA iz družine Spartan3A in vmesnik USB PIC za programiranje. Vezava in programska oprema temelji na odprti arhitekturi (open-source) Xess XuLA-50. Na plošči je tudi oscilator, statični pomnilnik in izhod za računalniški monitor VGA. Prva izvedba je bila razvita v okviru diplomske naloge Damjana Reparja uporabljali pa jo bomo za Tekmovanje v načrtovanju vezij 2012/13. Lastnosti:

|  |

Kratka navodila za uporabo

Razvojni modul se napaja preko povezave USB z osebnim računalnikom. Na plošči je tudi priključek za napajanje brez povezave z računalnikom, vendar mora biti v tem primeru kratkospojnik JP1 OBVEZNO izključen, sicer lahko pride napajalna napetost v računalnik. Ob priklopu na USB nekaj časa utripa in potem sveti LEDU, kar označuje pripravljenost vezja na programiranje. Če LED ne zasveti, pomeni da na računalniku ni nameščen gonilnik ali pa je kaj narobe z PIC/USB povezavo.

Programiranje vezja FPGA

Programsko opremo in gonilnik namestite s spletne strani Xess downloads, kjer izberite orodje XSTOOLs. Programiranje modula izvajamo z orodjem GXSLOAD, ki se pojavi ob namestitvi XSTOOLs. V programu GXSLOAD izberemo vrsto plošče XuLA-50, z miško prenesemo nastavitveno datoteko nastavitveno datoteko (*.bit) v okence FPGA/CPLD in kliknemo Load za programiranje vezja.

Dokumenti in datoteke

Shema razvojne plošče

Shema plošče v datoteki S3Ashema.pdf.

Programska oprema

XSTOOLS je brezplačno dostopna na spletni strani Xess downloads.

Referenčni primer: test oscilatorjev, LED in VGA

V orodju Xilinx ISE nastavimo pri izdelavi novega projekta vezje iz družine Spartan-3A, XC3S50A v ohišju VQ100. Referenčno vezje GrafikaS3.zip vsebuje delilnik ure, ki povzroči utripanje LED2, generator sinhronizacijskih signalov za izhod VGA in logiko za izris barvnih prog na monitorju. Vse izvorne datoteke (*.vhd in *.ucf) je potrebno dodati v projekt programa ISE in narediti sinteto ter implementacijo vezja. Pri Generate Programming File v Properties nastavimo v kategoriji Startup Options lastnost FPGA Start-Up Clock na JTAG. Potrdimo nastavitve in z dvojnim klikom izvedemo Generate Programming File, ki naredi datoteko s kočnico bit za programiranje vezja.