Laboratorij za načrtovanje integriranih vezij - Fakulteta za elektrotehniko, Ljubljana

Navodila za Xilinx ISE in ModelSim

1. Namestitev ISE in ModelSim | 2. Osnove Xilinx ISE | 3. Osnove ModelSimNamestitev razvojnega orodja Xilinx ISE Webpack in ModelSim

1. FPGA razvojno okolje Xilinx ISE

Podjetje Xilinx ponuja na svoji spletni strani osnovno verzijo razvojnega okolja za njihova FPGA in CPLD vezja. Dostop do brezplačnega proramskega paketa ISE WebPACK dobite, če na njihovi strani opravite registracijo. Geslo za dostop pošljejo po elektronski pošti. V laboratoriju LRNV je trenutno nameščena verzija 10.1, ki potrebuje > 5 GB prostora na disku.Starejšo verzijo WebPACK 6.3 (Project Navigator), ki zasede le okoli 0.5 GB, lahko naložite iz našega strežnika:

- WebPACK v6.3 (202MB, geslo za dostop dobite na laboratorijskih vajah)

- Service Pack v6.3.03 (268MB, geslo za dostop dobite na laboratorijskih vajah)

2. VHDL simulator

V vseh novejših verzijah Xilinx ISE (V10 ali višje) vključuje simulator. Kratka navodila za uporabo.

Programski paket ModelSim Xilinx Edition od decembra 2010 žal ni več dostopen na strani proizvajalca Xilinx in zanj tudi ne dajejo več brezplačnih licenc.

- MXE_3_63C.zip (200MB, za Windows Vista, licence niso več dostopne)

- MXE_6.0a.exe (102MB, starejša verzija za Windows XP, licence niso več dostopne)

3. Vprašanja in odgovori

Zakaj ISE simulator ob zagonu javi napako "ERROR: Signal Unknown signal received" in se ne požene?

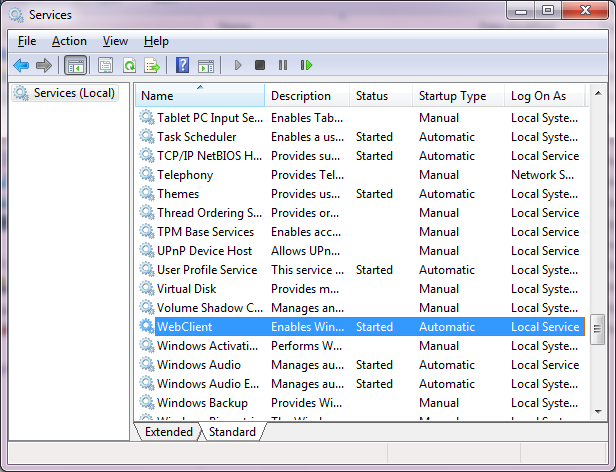

- Težava je pri verziji ISE 10.1 v Windows 7. Poskusite v nadzorni plošči oken ročno zagnati WebClient service. Glej odgovor: ISE-10-1-simulation-error

Zakaj ne dobim licence za Modelsim, čeprav sem se registriral na www.xilinx.com?

- ModelSim lahko uporabljate le, če imate starejšo licenco (pridobljeno pred decembrom 2010). Orodje ModelSim z brezplačnimi licencami od decembra 2010 ni več podprto.

Kako naredim nov projekt za Xilinx ISE V8.1 ali višje?

- Izberi File->New Project in določi Project Location in Project Name.

- V naslednjem oknu izberi po vrsti: All, Spartan3, XC3S200, TQ144, -5.

Nastavi Synthesis Tool: XST (VHDL/Verilog) in Simulator: Modelsim-XE VHDL - V oknu Create New Source klikni gumb New Sorce, napiši ime datoteke, na levi strani izberi VHDL Module in v naslednjem oknu nastavi imena ter vrsto vhodnih in izhodnih signalov.

- Klikni Finish in v naslednjih oknih Next in Finish, da prideš do konca. Sledi pisanje VHDL kode ...

Zakaj v oknu Processes ne vidim opcij: Synthesize, Implement ...?

Najbolj pogost razlog je, da v oknu Sources ni izbrana VHDL

datoteka z opisom vezja. Klikni na ime datoteke, tako da bo osenčena.

Če to ne deluje poskusi naslednje:

- V oknu Sources for klikni na zavihek Libraries in v knjižnici work poišči ime VHDL datoteke. Klikni z desnim gumbom na ime datoteke, izberi Properties in nastavi Association na Synthesis/Imp + Simulation

- V oknu Sources for izberi Synthesis/Implementation. Spodaj izberi zavihek Sources in enkrat klikni na ime VHDL datoteke, na kateri želiš delati sintezo, preverjanje sintakse in implementacijo.

Kako povežem Modelsim simulator iz Xilinx ISE V8.1 ali višje?

- V programu Xilinx ISE izberi Edit->Preferences in v ISE General klikni na Integrated Tools. Nastavi pot za Model Tech Simulator: C:\...\win32pe\modelsim.exe

- Preveri, če je kot privzeti simulator za projekt nastavljen Modelsim-XE VHDL (glej prvo vprašanje). Okno za nastavljenje simulatorja se odpre, če z desnim gumbom klikneš na ime FPGA vezja (xc3s200-5TQ144) v oknu Sources for.

Kako poženem simulator Modelsim iz programa Xilinx ISE V8.1 ali višje?

- Za nastavitev glej prejšnje vprašanje.

- V oknu Sources for izberi Behavioral Simulation in enkrat klikni na ime VHDL datoteke.

- V oknu Processes sedaj lahko izbereš Modelsim Simulator, Simulate...

Ali moram program Modelsim po vsaki spremembi VHDL kode zapreti in ponovno zagnati?

- Da, ker je to najlažja pot. Pri zagonu iz programa Xilinx ISE se izvrši avtomatsko prevajanje in inicializacija simulatorja.

- Ne, vendar je v tem primeru potrebno ročno izvršiti prevajanje in ponovni zagon simulatorja. V oknu Workspace izberi zavihek Library in klikni na + pri knjižnici z imenom work. Z desnim gumbom klikni na ime vezja in izberi Recompile. Nato ponovno poženi simulator Simulate->Run->Restart in nastavi vhodne signale.