Fakulteta za elektrotehniko -

Tržaška 25 - 1000 Ljubljana - Slovenija

Laboratorij za načrtovanje integriranih vezij

Tel: +386 1 4768 351

Predmeti

1. stopnja

2. stopnja

3. stopnja

Dodiplomski (stari)

Podiplomski (stari)

Projekti in diplome

Razvojno orodje za vezja FPGA

Kratka navodila za delo s programsko opremo Xilinx ISE 12

Proizvajalci programirljivih vezij ponujajo razvojna orodja, ki so v osnovni izvedbi brezplačna. Podjetje Xilinx ponuja na svoji spletni strani programsko opremo ISE Design Suite, ki jo dobite brezplačno, če na njihovi strani opravite registracijo. Geslo za dostop pošljejo po elektronski pošti. Njihovo najnovejše orodje z oznako Vivado podpira le vezja FPGA serije 7 in novejša.

V laboratoriju LRNV je trenutno nameščena programska oprema ISE V12.4, ki deluje na operacijskih sistemih Windows (32 in 64-bitni do verzije 7) in RedHat Linux. Namestite lahko tudi novejše verzije ISE (14.6), ki uradne podpore za Windows 8 nimajo, obstajajo pa nasveti na forumih glede namestitve.

Ob namestitvi ISE Design Suite obvezno izberite različico ISE WebPACK (Free), saj ostale zahtevajo za delovanje plačljivo licenco.

Osnove orodja Xilinx ISE Project Navigator

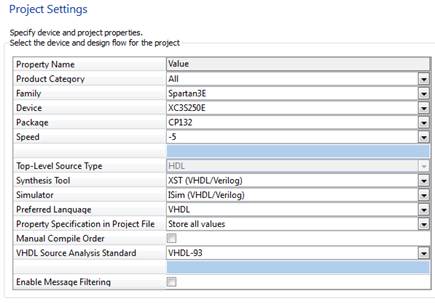

Izdelava novega projektaRazvojno okolje odpremo s klikom na ikono ISE Project Navigator. V meniju File izberemo New Project. Odpre se novo okno "New Project Wizard" v katerem nastavimo ime projekta, lokacijo na disku in vrsto. Najprej izberemo lokacijo, npr. C:\users\vaje\Andrej, nato pa ime projekta, npr. Log_vrata. Program bo na disku ustvaril novo mapo (C:\users\vaje\Andrej\Log_vrata) v kateri bodo vse datoteke. Imeni mape in projekta naj ne vsebujeta šumnikov ter presledkov, da ne bo težav pri prevajanju kode. V naslednjem oknu z oznako "Project Settings" nastavimo vrsto programirljivega vezja: najprej družino (Family), nato element (Device) in ohišje (Package). |

|

|

Nastavitev za vezje XC3S250E na plošči Basys2 je prikazana na sliki. Ob kliku na gumb naprej odpremo nov prazen projekt. Program Project Navigator omogoča različne načine vnosa vezja: od pripravljenih jeder IP in risanja sheme do pisanja kode v jeziku VHDL ali Verilog. Za začetek si pomagajmo si s čarovnikom New Source Wizard, ki za zaženemo s klikom na ikono New Source ali iz menija Project > New Source. V oknu najprej določimo ime datoteke (File name) in izberemo vrsto, npr. VHDL module. V naslednjem koraku se odpre tabela, kjer določimo imena in vrsto zunanjih signalov. Če je signal večbitni vektor, naredimo kljukico pri Bus in določimo velikost vektorja – nastavljali bomo le vrednost MSB, LSB pa naj bo vedno na 0. Ko so definirani vsi zunanji signali, zaključimo postopek (Next in Finish). V urejevalniku se odpre ogrodje VHDL opisa vezja z definiranimi priključki, ki ga dopolnimo z opisom vezja. Ko je opis dokončan, naredimo sintezo vezja in simulacijo. | |

Koraki tehnološke implementacije

|

Sinteza vezjaNajprej poskrbimo, da je izbran implementacijski pogled (View: Implementation) in da je označena datoteka z opisom vezja, ki ga želimo prevajati. Nato v zavihku Processes z dvojnim klikom na Synthesize-XST poženemo sintezo vezja. Če želimo najprej poiskati sintaktične napake, s klikom na + odpremo Synthesize in dvokliknemo na Check Syntax. Med sintezo program izpisuje poročilo v konzolo, kjer lahko preberemo opis morebitnih napak in opozoril (warning). Za razumevanje kakšno vezje je nastalo ob sintezi je zelo uporaben del poročila, ki opisuje najdene makro gradnike (npr. registri, seštevalniki). |

|

Preden zaženemo postopek implementacije vezja moramo v datoteki UCF določiti mesta priključkov, ki so za laboratorijsko ploščo opisana v dokumentu Basys2 reference manual. Naredimo novo izvorno datoteko (New Source) vrste Implementation Constraints File. V tej datoteki v vsako vrstico zapišemo mesto enega izmed zunanjih signalov oz. priključkov vezja, npr: NET "clk" LOC = "M6"; NET "koda<0>" LOC = "P11"; NET "koda<1>" LOC = "L3"; | |

Osnove simulatorja ISim

Izvedba simulacije vezja brez testne strukture | |

|

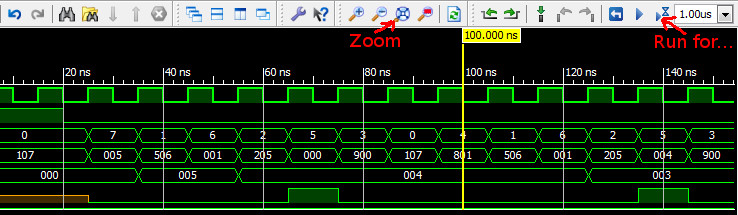

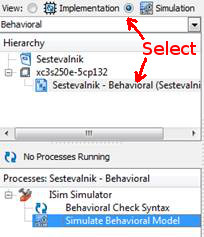

Za simulacijo kompleksnih vezij potrebujemo testno strukturo, ki opisuje spreminjanje vhodnih signalov, tako da ob zagonu simulatorja le še pregledamo rezultate. Preproste gradnika pa simuliramo kar s sprotnim nastavljanjem vrednosti vhodov in izvajanjem simulacije po korakih. Najprej v okolju ISE spremenimo pogled (View: Simulation) in poskrbimo, da je označena datoteka z opisom vezja, ki ga želimo simulirati. V procesnem oknu s klikom na + odpremo ISim Simulator in poženemo simulacijo z dvojnim klikom na Simulate Behavioral Model. Ko se odpre simulacijsko okno, odpremo meni za nastavljanje vhodnih vrednosti z desnim klikom na ime signala. Iz menija izberemo opcijo: Force Constant… ali če nastavljamo uro Force Clock… V polje Force to Value vnesemo vrednost v obliki kot ga določa polje Value Radix (privzeta oblika je dvojiški zapis). Ko kliknemo na OK se v konzoli izvede ustrezen ukaz, sprememba vrednosti signala pa bo vidna šele ko poženemo simulacijo. |

|

Simulator poženemo s klikom na ikono Run for in sicer za časovni korak, ki je določen v oknu za to ikono. Kadar izvajamo simulacijo po korakih, sledi temu ponovna nastavitev vhodov in naslednji korak. Pri pregledu rezultatov simulacije uporabimo ikone za zumiranje in nastavimo obliko izpisa signalov. Če nam privzeta oblika prikaza vrednosti ne ustreza, izberemo signal, z desnim klikom iz menuja opcijo Radix ter izberemo: Binary, Unsigned Decimal…