Andrej Trost

Assistant Professor, Electrical Engineering,

University of Ljubljana, Faculty of Electrical Enginering,

Laboratory for Integrated Circuits Design,

Trzaska 25, 1000 Ljubljana, Slovenia

Phone: (+386 1) 4768 350

E-mail: Andrej.Trost@fe.uni-lj.si

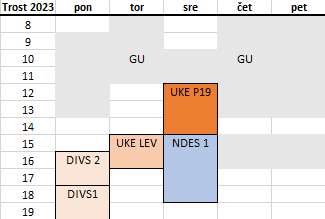

Office hours / Govorilne ure: Vsak torek ob 10h in četrtek ob 10h v četrtem nadstropju (B405), oziroma po dogovoru na Zoom

Lecturing courses: Digital Electronic Systems (1st level - UNI), Programmable Digital Systems (1st level - VS) and co-lecturing Design of Digital Electronics Systems (3th, postgraduate).

Assistant at Module B IC/DDES (1st level - VS), Testing of electronic circuits (2st level - UNI) and Digital Integrated Circuits and Systems (2nd level - UNI).

I am a mentor to several students working on diploma, masters and PhD theses at the Laboratory for integrated circuit design.

I was born 13. 8. 1972 in Ljubljana, where I attended primary school Trnovo in years 1979/87 and secondary school Gimnazija Bezigrad in 1987/91. In 1991 I applied at the Faculty of Electrical Engineering (FE), University of Ljubljana and chose Electronics program. I graduated with a degree in Electrical Engineering in 1995 and received MSc and PhD degrees in 1998 and 2000 respectively. In 1996 I was three months visiting (project PROTEUS) faculty ESIEE in Paris, France, and working on VHDL design of digital circuits for real-time image segmentation. I am working at Laboratory of integrated circuit design (LNIV). At the University of Ljubljana I was elected in 2001 an Assistant Professor and in 2012 an Associate Professor of Electrical Engineering.

My research areas are design of digital circuits and systems in FPGA technology and development of digital design tools used for teaching and research purposes. At the FE I developed several educational digital design tools: hardware verification system, graphical test bench tool and simplified hardware description language (HDL) with online tool. We are using development tools from Xilinx and Intel (Altera) targeting their FPGA and System-on-Chip (SoC) devices. I am currenty involved in high-level design of digital circuits with VHDL, Verilog or C-synthesis for real-time applications in digital signal and data processing: image pipeline and neural networks. With LNIV we are developing custom hardware and applications for SoC devices implementing digital signal processing on RedPitaya boards.

At the Faculty of Electrical

Engineering I am lecturing elective courses: Digital Electronic Systems,

Programmable Digital Systems, Design of Digital Electronics Systems and

work as an assistant on several courses (Integrated circuits, Testing of

Electronic Circuits, Digital Integrated Circuits and Systems).

I am mentoring students working at the LNIV on the topics of

electronics circuit design, high-level digital design, simulation

and implementation on FPGA devices. I am involved in organisation of

seminars, summer schools, workshops, scientific conferences

(ERK) and competition on

digital circuits design. I led several industrial projects and prepared

seminars for Slovenian electronics industry. In 2002 and 2012 I received Faculty Vidmar award for assistants.

I was a Chair of IEEE Slovenia section in 2018-2021. I am an editor of a scientific Journal

Elektrotehniški vestnik.

(c) LNIV 2022