Gradivo na naslednjih straneh predstavlja najbolj osnovne koncepte jezika VHDL. Sintaksa jezika je opisana na primerih tipičnih digitalnih vezij, od preprostih vezij (izbiralniki, primerjalniki, flip-flopi) do kompleksnejših vezij kot so sekvenčni avtomati in osnov strukturnega načrtovanja. Primeri vezij so povzeti iz učbenika za laboratorijske vaje pri predmetih Integrirana vezja, Digitalni elektronski sistemi in izbirnem modulu B: IV / NDES.

Ob nekaterih primerih so ikone, ki ob kliku ponudijo okno z dodatno razlago sintakse, posebnosti simulacije in pravil kodiranja v jeziku VHDL za sintezo vezja :

Več informacij in razlage najdete v učbeniku:

- A. Trost, "Načrtovanje digitalnih vezij v jeziku VHDL", založba FE/FRI, 2011

2.1 Vmesnik, arhitektura in signali

Model digitalnega vezja ali sistema v jeziku VHDL je sestavljen iz dveh glavnih delov:

- v vmesniku (entity) so opisani zunanji signali

- v zgradbi (architecture) pa je opisano delovanje vezja.

Zgradba modela vezja

entity ime_vezja is -- vmesnik

port (...);

-- deklaracija zunanjih signalov

end ime_vezja;

architecture opis_vezja of ime_vezja is

signal ime: tip_signala; -- notranji signali

...

begin

stavki ...

end opis_vezja;

Osnovni elementi opisa vezja so signali. V vmesniku določimo ime vezja in naredimo deklaracijo zunanjih signalov (stavek port). Znotraj arhitekturnega dela deklariramo notranje signale in zapišemo stavke, ki določajo kaj se dogaja s signali vezja. Zunanjim signalom moramo določiti smer in podatkovni tip:

Opis zunanjih signalov

port ( ime: smer tip_signala;ime1, ime2: smer tip_signala;

...

);

smer: in vhodni signal

out

izhodni signal

buffer

izhodni in notranji signal

inout

dvosmerni signal

tip_signala: bit, bit_vector, std_logic ...

- Vhodni signali se uporabljajo za branje vrednosti (na desni prireditvenih stavkov ali v pogojih), ne moremo pa jim določati vrednosti,

- izhodnim signalom določamo vrednosti v prireditvenih stavkih, ne moremo pa jih brati,

- signali tipa buffer so izhodi, ki jim določamo vrednost in jih lahko tudi beremo (so na obeh straneh prireditvenih stavkov),

- dvosmerne signale potrebujemo za opis posebnih zunanjih vodil, ki so obenem vhodi in izhodi.

Podatkovni tip

Osnovna podatkovna tipa, ki predstavljata signale (povezave) v vezju sta bit in std_logic. Signali tipa bit lahko zavzamejo le vrednost logične ničle ali enice. Za simulacijo je bolj primeren podatkovni tip std_logic, ker vsebuje tudi nedefinirano stanje 'U', kratek stik 'X', stanje visoke impedance 'Z' itd. Ta podatkovni tip ni vnaprej definiran, zato moramo pri njegovi uporabi v opis vezja vključiti knjižnico IEEE.std_logic_1164. Knjižnica vsebuje definicijo podatkovnega tipa std_logic in vseh logičnih operacij (z vsemi možnimi vrednostmi).

Več signalov združujemo v vodila, za katere uporabljamo v jeziku VHDL vektorske podatkovne tipe: bit_vector in std_logic_vector. Velikost vektorjev določimo pri deklaraciji kjer navedemo indeksa spodnje in zgornje meje. Najnižji bit ima običajno indeks 0 in se nahaja na desni strani, zato npr. 8-bitni vektor deklariramo kot: (7 downto 0).

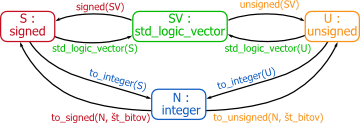

Vrednost vektorja je dvojiško število, ki ga lahko interpretiramo kot celo število s predznakom ali brez predznaka. Za nedvoumno interpretacijo vrednosti uporabimo vektorski tip signed ali unsigned iz numerične knjižnice IEEE.numeric_std. Tam so definirane tudi vse osnovne aritmetične operacije s celoštevilskimi vektorji. Podatkovni tip integer predstavlja 32 bitna cela števila in se uporablja pri računskih operacijah, v primerjalnih izrazih in za indeksiranje vektorjev.

Vektorji

Deklaracija: a: std_logic_vector (7 downto 0)Prirejanje vrednosti: a <= "01011001"

Posamezni element vektorja: a(7) = '0'

Podvektor: a(3 downto 0) = "1001"

Jezik VHDL zahteva, da zapišemo pretvorbo podatkovnih tipov v vseh izrazih, kjer se pojavljajo signali različnih tipov. Izjema so izrazi z nekaterimi računskimi operatorji (seštevanje, odštevanje, množenje) in primerjalnimi operatorji, kjer je pretvorba definirana v knjižnicah. Prireditveni izrazi pa vedno zahtevajo eksplicitno pretvorbo:

signal a,b,c: std_logic_vector(7 downto 0);signal vsota: unsigned(7 downto 0);

...

-- a in b pred seštevanjem pretvorimo v unsigned

vsota <= unsigned(a) + unsigned(b);

c <= std_logic_vector(vsota);

| Model vezja |

Naredimo model vezja, ki generira učinek leteče luči. Na vhodu vezja je ura (clk) in dva kontronlna signala (ena in neg), izhod pa je 4-biten vektor (luc).

Kadar izdelujemo novo izvorno datoteko (New Source) določimo vrsto datoteke: VHDL Module. Programska oprema bo avtomatsko odprla čarovnik (wizzard), ki nam pomaga pri prvih korakih sestavljanja modela vezja. Določiti moramo ime datoteke z opisom vezja, ime vezja in arhitekture ter imena in vrsto zunanjih signalov. Program bo avtomatsko sestavil datoteko z vmesnikom in praznim arhitekturnim stavkom. V naslednjih korakih moramo le še dopolniti arhitekturni del z deklaracijami notranjih signalov in stavki, ki opisujejo delovanje vezja.

Celoten opis vezja:

|

library IEEE; use IEEE.std_logic_1164.all; -- definicija std_logic_vector use IEEE.numeric_std.all; -- def. unsigned in seštevanja |

|

|

entity LetLuc is Port ( clk : in STD_LOGIC; ena : in STD_LOGIC; neg : in STD_LOGIC; luc : out STD_LOGIC_VECTOR (3 downto 0)); end LetLuc; |

zunanji signali |

|

architecture Opis of LetLuc is signal st: unsigned (1 downto 0):="00"; signal komb: std_logic_vector (3 downto 0); begin | notranji signali |

|

Kontr: process(clk) begin if rising_edge(clk) and ena='1' then st <= st + 1; end if; end process; | sekvenčni proces |

|

Log: process(st) begin if st="00" then komb <= "1000"; elsif st="01" then komb <= "0100"; elsif st="10" then komb <= "0010"; else komb <= "0001"; end if; end process; | kombinacijski proces |

|

luc <= komb when neg='0' else not komb; end Opis; |

prireditveni stavek |

| Osnovni stavki |  |