Laboratorij za načrtovanje integriranih vezij - Fakulteta za elektrotehniko, Ljubljana

Navodila za Xilinx ISE in ModelSim

1. Namestitev ISE in ModelSim | 2. Osnove Xilinx ISE | 3. Simulacija vezja | 4. Digilent orodja | 5. StateCADNavodila za izdelavo diagrama stanj

Orodje StateCAD

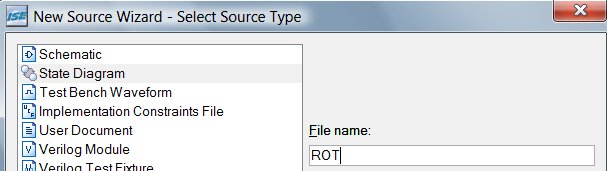

V programu Xilinx ISE naredimo novo datoteko Project > New Source in izberemo opcijo State Diagram ter določimo ime diagrama.

Ko program prvič poženemo, preverimo in po potrebi spremenimo nastavitve, da bodo izhodne datoteke v pravilnem formatu. Iz menuja Options izberemo Configuration in nastavimo opciji Language: VHDL in Language Vendor: Xilinx XST.

1. Priprava diagrama

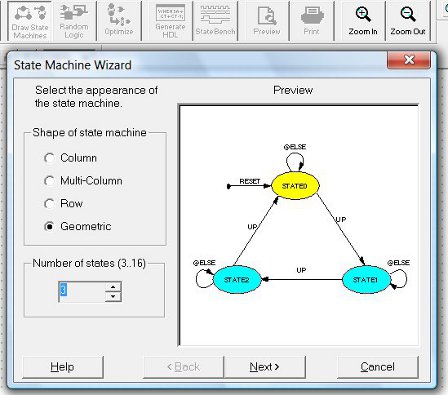

V programu StateCAD lahko na hitro pripravimo ogrodje diagrama stanj s klikom na ikono Draw State Machines. Odpre se čarovnik (State Machine Wizzard) v katerem najprej izberemo obliko diagrama in število stanj. Nato kliknemo na gumb Next in v naslednjem oknu izberemo vrsto reset signala (npr. sinhroni). V zadnjem oknu določimo kakšne vrste prehodov naj ima vsako stanje: Loop back pomeni ohranjanje stanja, Next so prehodi v naslednje stanje, Previous pa prehodi v prejšnje stanje. Prehode lahko dodamo ali izbrišemo tudi kasneje. Nato kliknemo na Finish in postavimo vzorec diagrama na list.

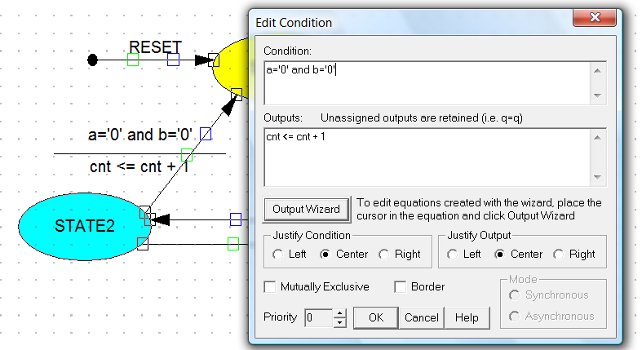

Ob dvojnem kliku na puščico, ki predstavlja prehod med stanji, se odpre okno. V okvirček Condition: zapišemo pogoj za prehod. Če naj se ob prehodu spremeni tudi kakšen izhodni signal, zapišemo ustrezno prireditev v okvirček Outputs.

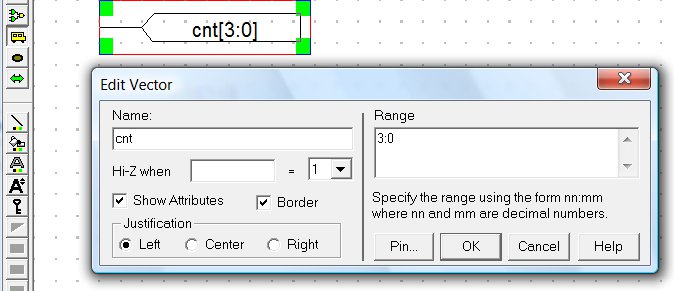

Vektorske signale dodamo s pritiskom na gumb Add Vector. Program avtomatsko nariše simbol za zunanji priključek. Ob kliku na simbol se odpre okno v katerem nastavimo ime, velikost (Range) in vrsto signala. Vse signale diagrama urejamo v oknu, ki se odpre s kombinacijo tipk Ctrl+E.

Ko zaključimo z risanjem diagrama kliknemo na gumb Generate HDL, ki sproži prevajanje (Compile) diagrama v HDL kodo