Laboratorij za načrtovanje integriranih vezij - Fakulteta za elektrotehniko, Ljubljana

Razvojni modul Spartan-3

1. Navodila za uporabo | 2. Izdelava razvojnega modulaOpis razvojnega modula Spartan-3

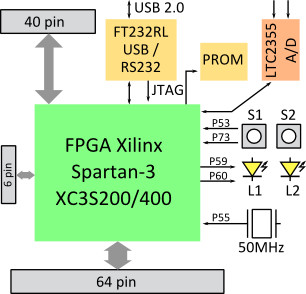

Spartan-3 razvojni modul je prototipno vezje, ki je razvito v celoti v Laboratoriju za načrtovanje integriranih vezij. Glavni gradnik modula je programirljivo vezje Xilinx Spartan-3 XC3S200 (ali 3S400) v ohišju TQ144. Modul vsebuje FT232 USB-RS232 vmesnik, ki omogoča tudi konfiguracijo modula. Zadnja različica modula (V2.0) je bila razvita za potrebe Tekmovanja v načrtovanju vezij 2009. Lastnosti:

|  |

Kratka navodila za uporabo

Razvojni modul se napaja preko adapterja z enosmerno napetostjo 6V-9V, pozitivni pol je na sredinskem priključku J1. Ob priklopu napajanja sveti LED z oznako 2.5V. Modul povežemo z računalnikom preko USB priključka. Ob prvi povezavi je potrebno naložiti gonilnike za FT232 USB-RS232 vmesnik s spletne strani proizvajalca FTDI.

Programiranje vezja FPGA

Programiranje modula izvajamo z orodjem Jtag09.exe - Configure Device. Program prenese nastavitveno datoteko (*.bit) v FPGA ali v vezje PROM. Med razvojem novega vezja običajno programiramo samo vezje FPGA, ko pa imamo delujoče vezje, naložimo nastavitveno datoteko v PROM. Program Jtag09 glede na postavitev kratkospojnikov ugotovi katero vezje želimo programirati. Za programiranje vezja FPGA mora biti kratkospojnik JP2 v položaju 2-3, kratkospojnik JP1 pa naj bo odstranjen.

V prgramu ISE izberemo ustrezne nastavitve z desnim klikom na Generate Programming File in izbiro Properties. Odpre se okno, kjer izberemo kategorijo Startup Options in nastavimo lastnost FPGA Start-Up Clock na JTAG Clock. Potrdimo nastavitve in z dvojnim klikom izvedemo Generate Programming File, ki naredi datoteko s kočnico bit za programiranje vezja. Po uspešnem programiranju se prižge dioda DONE.

Programiranje vezja PROM

Naredimo implementacijo vezja in pod Generate Programming File v Properties nastavimo v kategoriji Startup Options lastnost FPGA Start-Up Clock na CCLK (to je sicer privzeta nastavitev pri novem projektu). Potrdimo nastavitve in z dvojnim klikom izvedemo še Generate Programming File, ki naredi datoteko s kočnico bit za programiranje vezja. Uporabite lahko datoteko leds2.bit za modul verzije V1.1 ali pa primer serijske komunikacije (glej razlago spodaj) rxtx2.bit za V2.0.

Za programiranje nastavimo kratkospojnik JP2 v položaj 1-2 in poženemo program Cofigure Device, ki bo ob uspešni detekciji javil Download PROM. Izberemo konfiguracijsko datoteko in sprožimo nalaganje, ki traja nekoliko dlje. Poskrbimo, da je kratkospojnik JP1 vstavljen (položaj 1-2) in izklopimo ter ponovno vklopimo napajanje, ki bo sprožilo nalaganje konfiguracije iz PROM. Brisanje in nalaganje konfiguracije lahko sprožimo tudi s pritiskom na tipko PROG v modulu verzije V1.1 ali s sklenitvijo JP1-3 (prog) v V2.0 na maso.

Serijska komunikacija

Gonilnik za FTDI USB vmesnik podpira direktno komunikacijo, ki jo uporablja program Jtag09, in navidezni USB-RS232 priključek, ki je uporaben za preprosto komunikacijo. Način delovanja se vzpostavi po priklopu USB kabla: če najprej poženemo program Jtag09, bo gonilnik deloval v direktnem načinu, če pa najprej poskusimo komunicirati preko RS232 pa bo preklopil v navidezni RS232 način. Za preklop med načinoma moramo vedno izklopiti in ponovno vklopiti USB kabel.

Dokumenti in datoteke

Shema razvojnega modula

Novejša shema (V2.0) Spartan3ModulV20.pdf in starejša verzija (V1.1) Spartan3ModulV11.pdf.

Program JTAG

Naloži program Jtag09.exe - Configure Device za programiranje vezij FPGA XC3S200, XC3S400 in Xilinx PROM na razvojnem modulu. Program potrebuje nameščen gonilnik proizvajalca FTDI. Ob zagonu se izvrši detekcija FTDI USB vmesnika, če vezje priklopimo kasneje pa moramo pritisniti gumb Connect. Ob uspešni detekciji program javi USB: Connected, eno vrstico nižje pa opiše identifikacijo JTAG verige v kateri je FPGA ali pa FPGA in PROM. Če javi napako, pomeni da je nekaj narobe z JTAG verigo (morda le kratkospojnik) ali s samo komunikacijo. Primer nastavitvene datoteke za modul verzije V1.1: leds1.bit.

Referenčni primer: test tipk in LED

V orodju Xilinx ISE nastavimo pri izdelavi novega projekta vezje iz družine Spartan-3, XC3S200 v ohišju TQ144. Referenčno vezje blink.vhd vsebuje delilnik ure, ki povzroči utripanje LED1, LED2 pa se prižge ob pritisku na tipko. Vezje opišemo (New Source, VHDL Module...) ter izvedemo sintezo in implementacijo. Pred postopkom implementacije ne pozabimo nastaviti lokacije vhodnih in izhodnih priključkov (User Constraints File).

|

#UCF lokacije pinov V2.0 NET "b1" LOC = "p53" ; NET "clk" LOC = "p55" ; NET "led1" LOC = "p60" ; NET "led2" LOC = "p59" ; |

#UCF lokacije pinov V1.1 NET "b1" LOC = "p69" ; NET "clk" LOC = "p55" ; NET "led1" LOC = "p76" ; NET "led2" LOC = "p73" ; |

Referenčni primer: serijska komunikacija

Preprost primer je narejen v projektu leds.zip z VHDL datoteko leds.vhd, ki ob pritisku na tipko odda črko S preko RS232. Za preizkus uporabimo nek terminalski program (npr. HyperTerminal, Termite...), ki ga nastavimo na 9600 baudov, 8 bitov, brez paritete in brez kontrole pretoka.

Tule pa so izvorne datoteke projekta RxTx2.zip, ki vsebuje oddajnik in sprejemnik RS232. Ob sprejemu znaka se takoj sproži oddajnik, ki ta znak pošlje nazaj na PC (9600 baudov, brez paritete). Oddajanje se sproži tudi ob pritisku na tipko, kot v prejšnjem primeru. Projekt vsebuje dve testni strukturi: t.vhd v kateri sta oddajnik in sprejemnik povezana, tako da ob simulaciji pritiska na tipko sprožimo oddajo in sprejem in TestRxTx.vhd z dvema zaporednima prenosoma na rx. Simulacije izvedite z nastavljenim časom okoli 5 ms.