[LNIV Xilinx](index.html) | [Vivado](vivado.htm) | blokovni diagram | [komponente IP](vivado-ip.htm) | [AXI IP](vivado-axi.htm) | [SW](sw.htm)

# Izdelava blokovnega diagrama

Povzetek korakov izdelave in prevajanja projekta z blokovnim diagramom v programu Vivado:

* začni nov projekt, definiraj Board

* Flow: Create Block Design, risanje sheme (Add IP)

* sinteza blokov: Generate Block Design (opcijsko)

* Create HDL Wrapper

* Run Implementation, Generate Bitstream

## Projekt

V programu Vivado izberi **Create Project**, določi ime, npr. `blok1` in lokacijo, npr. `C:/proj/moja_mapa`.

Pri izbiri imena in lokacije ne uporabljaj šumnikov in presledkov!

Nato 4-krat klikni Next, da ostanejo privzete opcije, na koncu pa določi **Default Part**

s klikom na gumb Boards in izbiro razvojne plošče.

*Vivado* pozna nekaj razvojnih plošč, nekatere pa je potrebno dodati, tako da kopiramo mapo z

opisom plošče v v inštalacijsko mapo: ```C:\Xilinx\Vivado\2019.1\data\boards\board_files\```.

Definicije razvojnih plošč:

* [MiniZed(zip)](board/minized.zip)

* [RedPitaya(zip)](RedPitayaBoard11.zip)

## Blokovni diagram

Blokovni diagram naredimo s klikom na **Create Block Design** v levem meniju.

Predstavili bomo primer blokovnega diagrama s knjižničnimi komponentami za razvojno ploščo

ZedBoard.

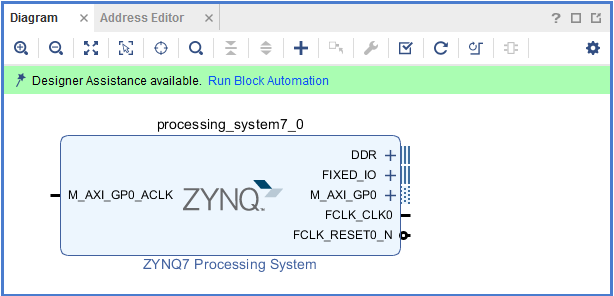

Klikni na Add IP (ikona + ali ctrl+i), v polje Search zapiši `Zynq` in izberi `ZYNQ7 Processing System`.

To je osnovna komponenta, ki predstavlja procesorski del vezij Zynq. Ko je komponenta postavljena na diagram,

jo po potrebi z dvoklikom nastavimo (Customize Block) in povežemo. Nekatere komponente zna program sam povezati

in ponudi pomoč na zelenem traku na vrhu diagrama (Designer Assistance available).

Če kliknemo na **Run Block Automation** in bo program avtomatsko naredil zunanje povezave procesorja (DDR in FIXED IO).

Procesorska komponenta ima priključke z vmesnikom AXI za povezavo z drugimi komponentami v vezju FPGA. Dodaj

v vezje vhodno-izhodni vmesnik AXI GPIO: Add IP in v Search vnesi `gpio`. Postavi komponento na diagrami

in z dvoklikom odpri okno za nastavitev parametrov.

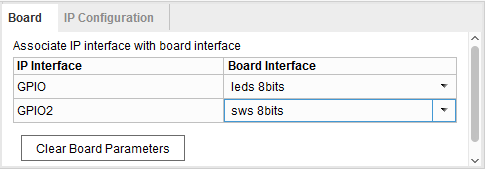

Vmesnik AXI GPIO ima en ali dva GPIO priključka, ki jima lahko v zavihku *IP Configuration* nastavimo število bitov

(1-32) in smer (All Inputs, All Outputs ali privzeto dvosmerni). V zavihku *Board* imamo možnost izbire specifične

nastavitve za izbrano razvojno ploščo. Izberi povezavo na LED in stikala:

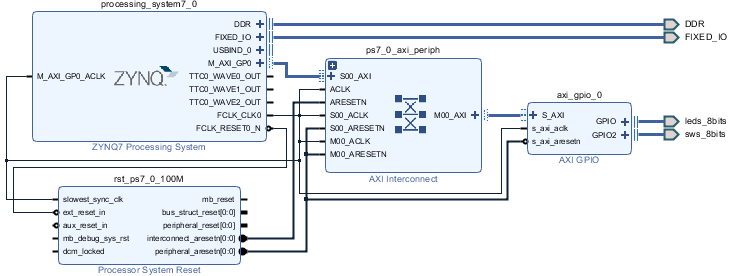

Na vrhu diagrama se ponovno pojavi zelen trak. Klikni na **Run Connection Automation** in izberi All Automation.

Program bo avtomatsko naredil zunanje povezave in dodal nekaj komponent za povezavo s procesorskim delom:

komponenta AXI Interconnect je vmesnik s pretvornikom protokola za vodilo AXI, komponenta Processor System Reset

pa pripravi ustrezno zaporedje resetirnih signalov za periferne enote. Celotna shema sedaj izgleda tako:

## Prevajanje

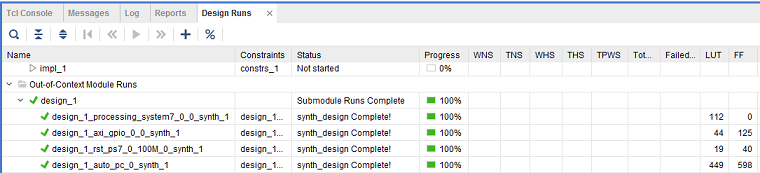

Blokovni diagram preveri z **Validate Design** (F6), nato klikni v levem meniju na **Generate Block Design** in gumb

Generate. Program bo iz repozitorija prenesel vse izvorne datoteke komponent IP in pognal sintezo. Trenutni

potek in rezultati so v spodnjem zavihku *Design Runs* pod Out-of-Context Module Runs:

V poročilu vidimo, da največ tabel (LUT) in flip-flopov (FF) zasede vmesnik s pretvornikom protokola AXI (design_1_auto_pc_0). Pred prevajanjem sistema je potrebno iz blokovnega diagrama narediti jezikovni opis

(HDL Wrapper). Izberi zavihek *Hierarchy* in v *Design Sources* z desnim gumbom klikni na datoteko diagrama

design_1, izberi **Create HDL Wrapper** ter potrdi privzeto izbiro (Let Vivado manage...).

Program bo glede na privzeti jezik projekta naredil novo VHDL ali Verilog datoteko, ki opisuje diagram.

Če je potrebno, pred prevajanjem dodamo v projekt še datoteke z omejitvami (Design Constraints), nato pa

prevedemo sistem: **Run Synthesis** in **Run Implementation**.

Po implementaciji izberemo Generate Bitstream, ki naredi nastavitveno datoteko za programirljivo vezje.