# Povprečevalno sito na Red Pitayi

Na razvojni plošči Red Pitaya naredimo vezje za skaliranje signalov in filtriranje z majhnim povprečevalnim

sitom, ki izračuna povprečje štirih zaporednih vzorcev.

Sistem je narejen podlagi odprte kode za FPGA [RedPitaya na GitHub] (https://github.com/RedPitaya/RedPitaya),

uporabili smo prvotno različico (classic). Izvorne datoteke predelanega projekta so v [RedPitaya2017.zip](http://lniv.fe.uni-lj.si/courses/div/RedPitaya2017.zip). Podmapa redpitaya vsebuje definicijo razvojne plošče za program Vivado in jo prenesemo

v inštalacijsko mapo: ```C:\Xilinx\Vivado\2016.4\data\boards\board_files\```

## Projekt

V Vivadu naredimo nov projekt za razvojno ploščo Red Pitaya in v mapo projekta vključimo podmape rtl, sdc in tcl. Podmapa

tcl vsebuje skripte za izdelavo blokovnega diagrama in vključitev izvornih datotek. Skripte so napisane za Vivado 2017.2,

izvedemo jih v zavihku Tcl Console:

- premakni se v trenutno mapo, npr: ```cd c:/proj/divs/redpitaya```

- naredi blokovni diagram: ```source tcl/system.tcl```

- in vključi ostale datoteke: ```source tcl/files.tcl```

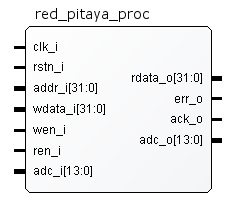

Priloženi projekt vsebuje vse izvorne komponente v jeziku [Verilog](../verilog/index.htm) in eno v jeziku VHDL, ki je namenjena opisu povprečevalnega sita.

Komponenta red_pitaya_proc.vhd je povezana na sistemsko vodilo (naslovni prostor: 0x405xxxxx) in na en vhodni podatkovni

kanal, ki pride iz A/D ali pa iz notranjega generatorja signalov (loopback). Signalni izhod je povezan na logiko osciloskopa,

da bomo lahko opazovali delovanje. Pomen signalov:

- clk_i, rstn_i: ura in reset signal (aktivna 0)

- sys_addr: 32-bitni naslovni vhod

- sys_wdata: 32-bitni vhodni podatek

- sys_wen, sys_ren: vhodna signala za branje in pisanje na vodilo

- adc_i: 14-bitni vhodni signal (1. kanal iz A/D)

- sys_rdata: 32-bitni izhodni podatek

- sys_err, sys_ack: izhoda za javljanje napake in potrditev prenosa

- adc_o: 14-bitni izhod, povezan na 1. kanal osciloskopa

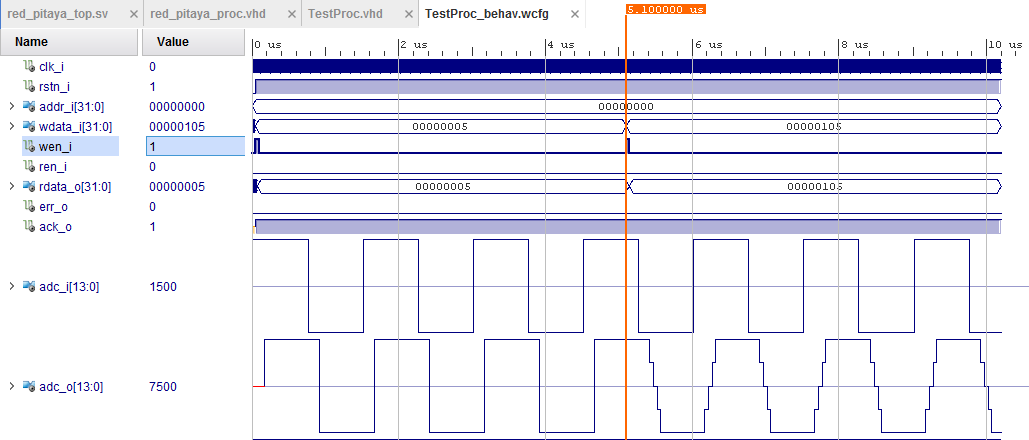

Opis logike komponente, ki izvaja operacijo skaliranja z našičenjem je v 7. vaji predmeta [Digitalna integrirana vezja in sistemi](http://lniv.fe.uni-lj.si/div.html). Testna struktura za simulacijo skaliranja: [TestProc.vhd](http://lniv.fe.uni-lj.si/courses/div/TestProc.vhd). Če naredimo poleg skaliranja še preprosto povprečevalno sito, ki računa povprečje štirih zaporednih vzorcev, dobimo rezultat

simulacije s pravokotnim vhodnim signalom:

Prvi del simulacije predstavlja le skaliran izhod, v drugem delu pa vidimo delovanje sita. Rezultat prevajanja je datoteka

red_pitaya_top.bit v podmapi ```<ime_projekta>.runs\impl_1```, ki jo prenesemo na razvojno ploščo.

## Razvojna plošča Red Pitaya

V laboratoriju LRNV bomo Red Pitayo priklopili kar neposredno na računalnikovo drugo omrežno kartico, ki jo nastavimo na lokalni naslov: 192.168.1.101. Red Pitaya bo dostopna na naslovu 192.168.1.15 v konzoli SSH programa PuTTY (ime: root, geslo: root).

S programom [WinSCP](https://winscp.net/eng/download.php) prenesemo datoteko red_pitaya_top.bit v lokalno mapo na Red Pitayo (npr. root),

nato pa jo v konzoli kopiramo v ustrezno mapo. V konzoli izvedemo:

- ```rw``` za omogočanje pisanja

- ```cp red_pitaya_top.bit /opt/redpitaya/fpga```

V spletni brskalnik napišemo naslov: 192.168.1.15 in poženemo aplikacijo Oscilloscope. Strežnik je nastavljen tako, da bo v FPGA naložil datoteko red_pitaya_top.bit. Testni signal za preizkus delovanja lahko dobimo kar iz generatorja signalov, ki ga nastavimo v aplikaciji.

Če vključimo loopback, bomo povezali izhod generatorja na vhod našega vezja kar znotraj FPGA: v konzoli nastavimo dva registra:

```

monitor 0x4000000c 1

monitor 0x40500000 2

```

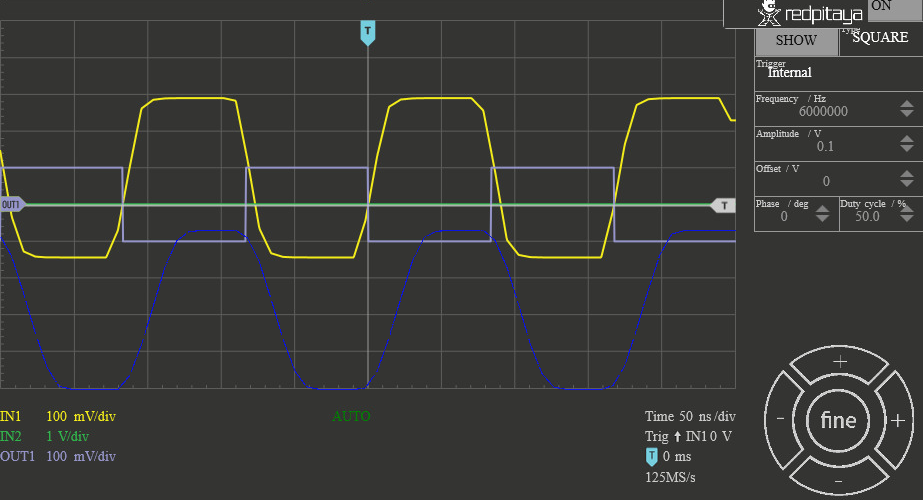

Prvi register nastavi loopback, drugi pa faktor skaliranja komponente red_pitaya_proc. Pri nastavljeni frekvenci 6 MHz vidimo delovanje

vhodnega sita osciloskopa - na sliki je pravokoten nastavljen (idealni) signal in realni signal rumene barve, ki je skaliran s faktorjem 2.

Če vključimo še povprečevalno sito dobimo signal z bolj položnim prehodom med logičnima stanjema (modri signal):

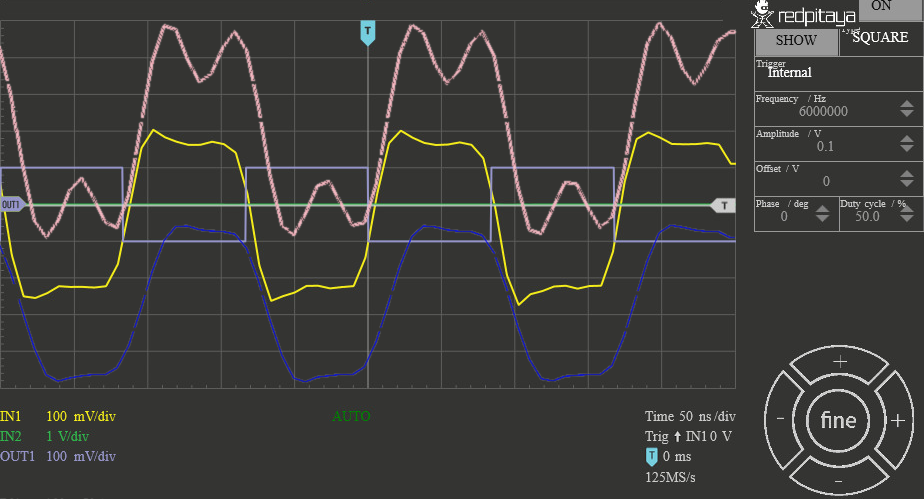

Rezultat obdelave zunanjega signala lahko opazujemo, če s kablom povežemo izhod D/A in vhod A/D prvega kanala. Na sliki smo združili tri

meritve:

- rumene barve je skaliran vhodni signal, ki ima nekaj prehodnih pojavov zaradi D/A in A/D pretvorbe,

- roza barve je vhodni signal, ki je povezan na izhod D/A brez zaključitve 50 Ohm in ima zato veliko oscilacij,

- modre barve pa je skaliran in filtriran vhod.