[LNIV Xilinx](index.html)

# Razvojna plošča [Red Pitaya](https://www.redpitaya.com/)

Red Pitaya je odprtokodna merilna platforma, ki temelji na SoC Xilinx Zynq. Strojne komponente so opisane v jeziku System Verilog in so dostopne na spletnem repozitoriju [GitHub](https://github.com/RedPitaya/RedPitaya-FPGA).

Projekt V0.94 je dobro izhodišče za razvoj modulov za obdelavo signalov po meri.

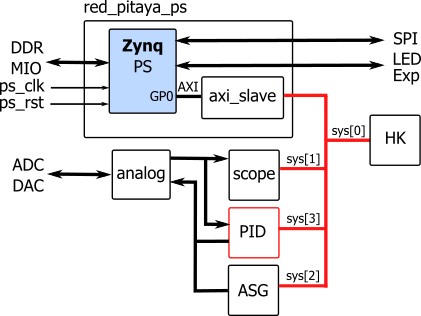

Vključuje periferne module za digitalni osciloskop, generator poljubnih signalov in PID regulator. Glavna komponenta povezuje procesni sistem (red_pitaya_ps) s perifernimi moduli, kot je predstavljeno v poenostavljenem blokovnem diagramu:

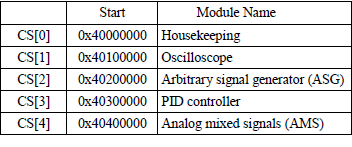

Procesor dostopa do zunanjih enot po vodilu AXI, kjer je naslovni prostor razdeljen na posamezne segmente.

Modul Housekeeping (red_pitaya_id.v) skrbi za ID in osnovne funkcije. Npr. Digital Loopback je na naslovu ```0x40 000 00C```.

Celoten seznam registrov vsebuje [Redpitaya Developer Guide](https://redpitaya.readthedocs.io/en/latest/developerGuide/devGuideTop.html).

V demonstracijskem projektu smo odstranili modula Daisy chain in PID, namesto PID pa vključili modul **proc**, ki je povezan tako z vhodnimi kot izhodnimi analognimi kanali. Procesni sistem krmili komponento prek preprostega sistemskega vodila (sys[3]).

## Projekt za Vitis 2025

- Razširi arhiv: [RP25.7z](./rp25/RP25.7z) v svojo projektno mapo. Izvorne datoteke v strojno-opisnem jeziku se nahajajo v podmapi sources.

- Projekt prevedi in naredi konfiguracijski bitstream, nato pa ga s TCL ukazi pretvori v utrezen format:

```

cd c:/proj/rp25

exec cp ./rp25.runs/impl_1/red_pitaya_top.bit ./proc.bit

bootgen -image proc.bif -arch zynq -process_bitstream bin -o proc.bit.bin -w

```

- Konfiguracijska datoteka proc.bit.bin je primerna za Red Pitayo z OS 2.0, za starejši OS pa uporabimo proc.bit. Programsko datoteko nastavimo z ukazom v terminalu:

```

./nastavi.sh proc.bit

```

ali

```

./nastavi2.sh proc.bit.bin

```

## Prenos na Red Pitayo

- V laboratoriju LRNV bomo Red Pitayo priklopili kar neposredno na računalnikovo drugo omrežno kartico, ki jo nastavimo na lokalni naslov: 192.168.1.101. Red Pitaya bo dostopna na naslovu 192.168.1.15 v konzoli SSH (ime in geslo: root).

- Z orodjem SFTP prenesi konfiguracijsko datoteko v lokalno mapo na Red Pitayo, nato pa v terminalskem oknu izvedi ukaz nastavi proc.bit (oz. nastavi2 proc.bit.bin), ki bo spremenil privzeto vsebino FPGA ob zagonu aplikacije Osciloskop.

- V spletni brskalnik napišemo naslov: 192.168.1.15 in poženemo aplikacijo Oscilloscope. Najprej preverimo delovanje vgrajene kode tako, da nastavimo prvi kanal signalnega generatorja.

Kliknemo na kolešček pri OUT1 in nato ON. Oscilogram bo prikazal sinusni izhod funkcijskega generatorja. Najprej bomo nastavili register Digital Loopback na 1, da bo signal generatorja povezan na vhod osciloskopa.

V programu Putty zapišemo ukaz:

```

monitor 0x4000000c 1

```

- Sedaj lahko preizkusimo delovanje našega vezja. Vezje, ki smo ga naredili namesto komponente PID ima registre na naslovih od ```0x40300050``` naprej.