[LNIV Xilinx](index.html)

# Oscilator na [Red Pitayi](https://www.redpitaya.com/)

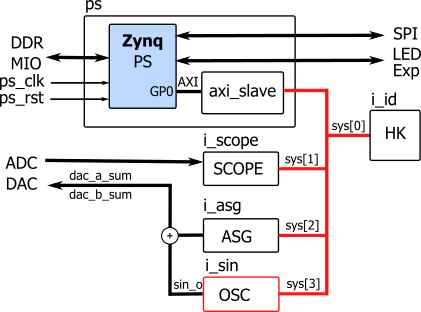

V digitalnem sistemu na Red Pitayi (classic) bomo zamenjali PID z modulom v katerem bo digitalni sinusni oscilator z nastavljivo frekvenco.

## Projekt za Vivado 2019

- Osnova je klasični projekt iz arhivskih datotek: [redpitaya-classic.zip](https://lniv.fe.uni-lj.si/courses/div/redpitaya-classic.zip), ki ga v Vivadu naložimo s skripto:

```

cd c:/proj/redpitaja

source ./make_project.tcl

```

V projekt bomo vključili še opis sinusnega oscilatorja s sistemskim vmesnikom in

ROM v katerem so zapisani vzorci sinusnega signala.

- Na koncu glavne datoteke red_pitaya_top.sv nadomesti modul PID z modulom red_pitaya_osc in ga poveži na

sistemsko vodilo

```

red_pitaya_osc i_sin (

.clk_i (adc_clk ), //ura

.rstn_i (adc_rstn ), //reset, aktiven ob 0

.sin_o (sin_o ), //14-bitni sinusni izhod

.addr_i (sys[3].addr ), //32-bitni naslov

.wdata_i (sys[3].wdata), //32-bitni vhodni podatek

.wen_i (sys[3].wen ), //omogoči vpis

.ren_i (sys[3].ren ), //omogoči branje

.rdata_o (sys[3].rdata), //32-bitni izhodni podatek

.err_o (sys[3].err ), //javi napako

.ack_o (sys[3].ack ) //potrdi prenos

);

```

- Sinusni izhodni signal deklariraj in poveži na en kanal izhodnega DAC, za test pa lahko tudi neposredno na en kanal osciloskopa, npr. .adc_a_i (sin_o)

```

wire [13:0] sin_o

assign dac_a_sum = asg_dat[0] + sin_o;

```

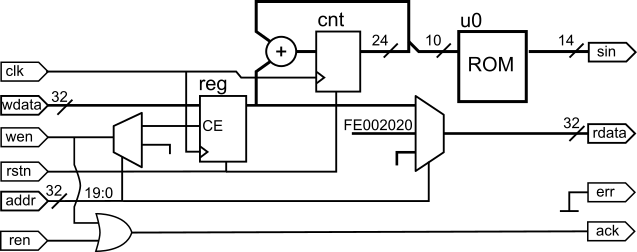

## Sinusni generator

Generator sinusnega signala sestavljajo vmesnik, števec in ROM s tabelirano eno periodo sinusa. Sinusni signal dobimo iz pomnilnika ROM, ki ga naslavlja 24-bitni števec **cnt** (naslov pomnilnika je zgornjih 8 ali 10 bitov števca). Števec se ob uri povečuje za vrednost zapisano v registru. Manjša vrednost registra povzroči daljši čas štetja in posledično nižjo izhodno frekvenco.

Vmesnik omogoča zapisovanje in branje vrednosti registrov iz sistemskega vodila Red Pitaye. Naslovni prostor je razdeljen

tako, da znoraj modula dekodiramo spodnjih 20 bitov naslova. Za nalogo lahko dodate registre s katerimi bi nastavljali

še amplitudo in ofset zunanjega signala.

### Model in simulacija v jeziku Verilog

Osnovni model sinusnega oscilatorja z registrom za nastavitev frekvence: [red_pitaya_osc.v](osc/red_pitaya_osc.v)

Model pomnilnika ROM z 256 vzorci 10-bitnega sinusnega signala: [rom.v](osc/rom.v)

```Verilog

always @(posedge clk_i)

begin

if (~rstn_i) begin

register <= 32'h00000000;

cnt <= 24'h000000;

end else begin

cnt <= cnt + register[23:0];

if (wen_i && (addr_i[19:0]==20'h10004)) begin

register <= wdata_i;

end

end

end

assign rom_addr = cnt[23:16];

rom u0(.adr(rom_addr), .data(rom_data));

assign data_o = rom_data;

```

Vmesnik sestavlja logika za branje identifikacije modula in registra ter pisanje vrednosti v register. Naslov registra smo

postavili na vrednost h10004, da ne bomo imeli konfliktov z aplikacijami na Red Pitayi, ki predvidevajo v tem naslovnem

prostoru komponento PID (naslovi registrov te komponente so nižje). Kadar procesor bere kakšen drug naslov, bo dobil vrnjeno

identifikacijsko vrednost FE002020.

- Preizkusi delovanje sinusnega generatorja s testno strukturo [test_osc.v](osc/test_osc.v) v kateri nastavi register na vrednost 10000. Uporabi simulator orodja Vivado ali pa odprtokodni simulator [Icarus Verilog](https://bleyer.org/icarus/)

s pregledovalnikom signalov **GTKWave**. Ukazi za prevajanje z orodjem Icarus in izvedbo simulacije:

```

iverilog -o test_osc test_osc.v red_pitaya_osc.v rom.v

vvp test_osc

```

### Model in simulacija v jeziku VHDL

Opis sinusnega oscilatorja s sistemskim vmesnikom: [red_pitaya_osc.vhd](osc/red_pitaya_osc.vhd)

Genrični ROM s 1024 vzorci 10-bitnega sinusnega signala: [rom.vhd](osc/rom.vhd)

- Preizkusi delovanje sinusnega generatorja s testno strukturo [osc_tb.vhd](osc/osc_tb.vhd) v kateri nastavi register na vrednost 10000. Uporabi simulator orodja Vivado ali pa odprtokodni simulator [GHDL](http://ghdl.free.fr/) s pregledovalnikom signalov [GTKWave](http://gtkwave.sourceforge.net/). Ukazi za prevajanje z orodjem GHDL in izvedbo simulacije:

```

ghdl -a rom.vhd

ghdl -a red_pitaya_osc.vhd

ghdl -a osc_tb.vhd

ghdl -r osc_tb --stop-time=2000ns --vcd=osc.vcd

```

Rezultat simulacije v programu GTKWave:

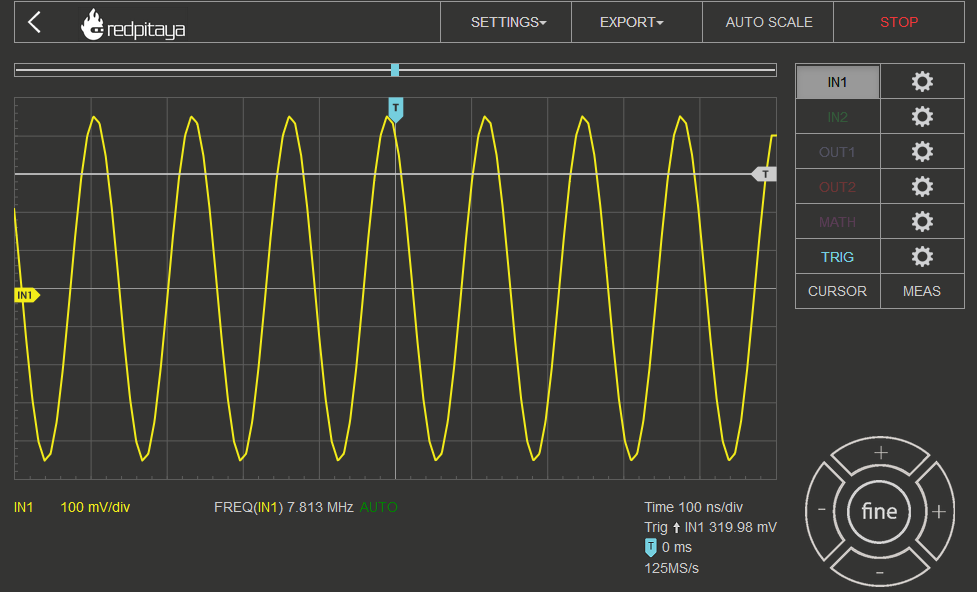

## Test na Red Pitayi

Po implementaciji digitalnega sistema z orodjem Vivado dobimo datoteko red_pitaya_top.bit, ki jo prenesemo na datotečni

sistem Red Pitaye. Delovanje generatorja na razvojni plošči najlažje opazujemo z aplikacijo osciloskop. Najprej moramo

aplikaciji povedati, da uporabi za programiranje FPGA našo datoteko. Nastavitev je zapisana v:

*/opt/redpitaya/www/apps/scopegenpro/fpga.conf*.

Ko v spletnem brskalniku poženemo osciloskop, se bo naložil FPGA iz datoteke na katero se sklicuje fpga.conf. Prepričajmo

se tako, da v konzoli preberemo identifikacijo:

```

monitor 0x40300000

```

ki mora vrniti vrednost FE002020. Nato nastavimo inkrement števca sinusnega generatorja, npr.:

```

monitor 0x40310004 100

```

in opazujemo izhodni signal: