[Home](index.html) | Vivado | [Blokovni diagram](vivado-blok.htm) | [Enostaven IP](vivado-ip.htm) | [AXI IP](vivado-axi.htm)

[SDK](sdk.htm)

# Osnove programa Vivado 2017

Predstavili bomo najbolj osnovne korake idelave RTL projekta v programu Xilinx Vivado 2017.

Projekt se nahaja v mapi, ki vsebuje datoteko z opisom projekta __projekt.xpr__

in podmape, med katerimi so:

* projekt.runs, mapa z rezultati sinteze (synth_1) in implementacije (impl_1)

* projekt.sdk, mapa procesorskega projekta (orodje SDK)

* projekt.sim, mapa s simulacijskimi datotekami

* projekt.srcs, mapa z izvornimi datotekami (sources_1) in omejitvami (constrs_1)

## Nov projekt

V programu Vivado 2017 izberi **Create Project**, določi ime, npr. `project_add` in lokacijo `D:/designs/moja_mapa`.

Pri izbiri imena in lokacije ne uporabljaj šumnikov in presledkov!

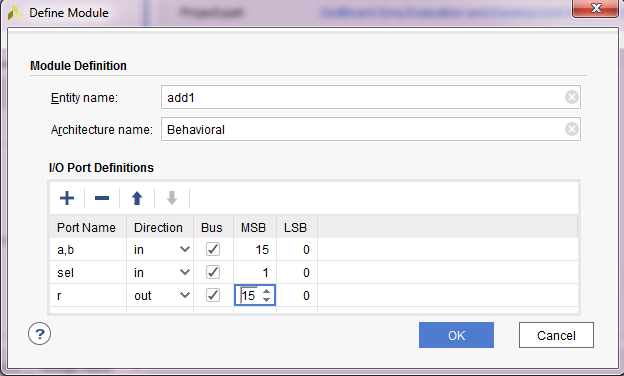

Klikni Next in pusti privzeto izbiro RTL Project. V naslednjem oknu **Add Sources**

klikni na Create File, izberi File type: `VHDL` in določi ime¸ npr. `add1`.

Klikni OK in dvakrat Next, na koncu pa določi ciljno integrirano vezje **Default Part**

ali ploščo (Boards). Po zadnji potrditvi se odpre tabela v kateri določi ime in zunanje priključke vezja:

Na podlagi vnešenih podatkov program naredi datoteko z ogrodjem opisa vezja v jeziku VDHL.

## Delo s projektom

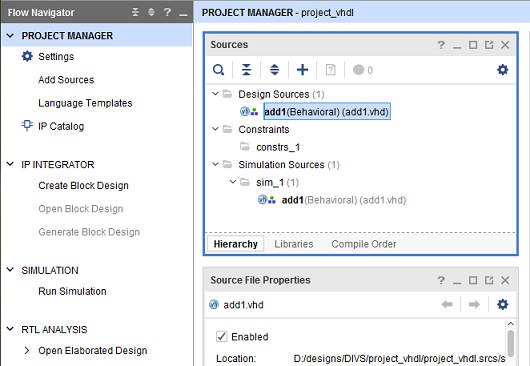

V programu Vivado uporabljamo pri delu s projektom naslednja okna:

* Flow Navigator na levi v obliki menija z glavnimi koraki izdelave in prevajanja projekta (ctrl+Q)

* Sources prikazuje hierarhijo izvornih datotek

* Properties prikazuje in omogoča nastavitve izbrane datoteke ali elementa blokovnega diagrama

* Poročila se nahajajo v spodnjem oknu z več zavihki, med katerimi je tudi konzola za ukaze Tcl

Izvorna datoteka, ki smo jo naredili s programom Vivado ali pa vključili kot Design Source

se pojavi v oknu **Sources** pod Design Sources in pod Simulation Sources.

Datoteko odpri z dvoklikom in dokončaj opis vezja:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity add1 is

Port ( a,b : in STD_LOGIC_VECTOR (15 downto 0);

sel : in STD_LOGIC_VECTOR (1 downto 0);

r : out STD_LOGIC_VECTOR (15 downto 0));

end add1;

architecture Behavioral of add1 is

signal a1,b1,r1: unsigned(15 downto 0);

begin

a1 <= unsigned(a);

b1 <= unsigned(b);

r1 <= a1 when sel="00" else

a1+1 when sel="01" else

a1+b1 when sel="10" else

a1-b1;

r <= std_logic_vector(r1);

end Behavioral;

```

Orodje Vivado že med tipkanjem kode opozarja na nekatere sintaktične napake in obarva ali podčrta

ustrezno vrstico ter izpiše sporočilo, če se z miško zadržimo nad označenim delom. Ko zaključimo

z opisom kode, shranimo datoteko in izvedemo analizo, prevajanje ali simulacijo.

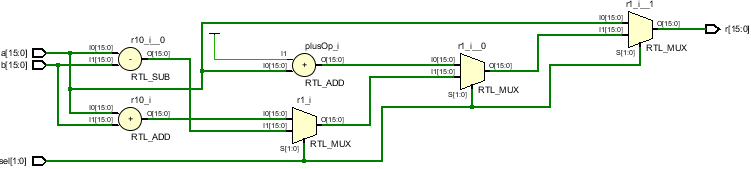

## Analiza vezja

Analiza vezja omogoča grafičen pregled gradnikov, ki nastanejo od prevajanju opisa vezja.

Postopek analize in izdelave sheme na nivoju registrov poženemo z **Open Elaborated Design** iz menija na levi.

Program bo začel izvajati sintezo vezja in prikazal shemo ali pa sporočilo o napakah, ki se pojavijo

tudi v spodnjem oknu v zavihku *Messages*.

Na shemi iz opisa našega vezja vidimo zunanje priključke, seštevalnike in izbiralnike:

## Simulacija

Simulacijo izvedemo z Run Simulation, Run Behavioral Simulation. Simulator prevede vezje in če ni napak

naredi izvršilno datoteko. Lahko se zgodi, da bo antivirusni program onemogočil izvajanje simulacije -

v tem primeru definirajmo izjemo za skeniranje mape s projektom.

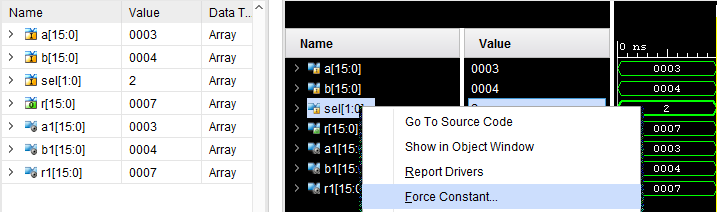

Enostavno simulacijo izvedemo tako, da nastavimo stimulatorje na vhodne signale, izvedemo simulacijo

za nek čas, spremenimo stimulatorje, ponovno izvedemo... S privzetimi nastavitvami v Vivadu se simulacija

avtomatsko izvede za 1000 ns in najbolje, da se najprej postavimo na začetek: Run > Restart.

V simulatorju z desnim klikom na vhodni signal nastavimo vrednost signala z izbiro Force Constant.

Za uro izberemo Force Clock in nastavimo kot npr.:

* Leading edge value: 0

* Trailing edge value: 1

* Period: 200 ns

Po opravljenih nastavitvah poženemo simulator za določen čas: Run > Run For in opazujemo izhode.

Prikaz oblikujemo tako, da izberemo enega ali več signalov, z desnim klikom izberemo Radix in

vrsto (Binary, Unsigned, Signed...). Vse nastavitve so vidne tudi v spodnjem oknu v zavihku *Tcl Console*.

Namesto klikanja z miško lahko v konzoli nastavljamo signale z ukazi. Poglejmo primer ukazov, ki nastavijo

signal *sel* na dvojiško vrednost 0, signal *a* na desetiško vrednost 9 in izvedejo simulacijo za 200 ns:

```tcl

add_force sel 0

add_force a -radix dec 9

run 200 ns

```

Če spremenimo datoteko VHDL je potrebno simulator ponovno zagnati z Run > Relaunch simulation, ki povzroči

ponovno prevajanje vezja. V primeru napak preverimo sporočila v zavihku *Tcl Console*.

Bolj obsežno simulacijo naredimo s testno strukturo v jeziku VHDL, ki jo moramo napisati sami ali

uporabiti kakšen program za grafično izdelavo testne strukture, kot je: [grafTB](http://lniv.fe.uni-lj.si/grafTB.htm)

ali avtomatično izdelavo ogrodja testne strukture, npr. [vhdl.lapinoo.net](http://vhdl.lapinoo.net/testbench/).

Datoteko s testno strukturo dodamo v projekt kot simulacijsko datoteko: **Add Sources**, Add or create simulation sources

in izvedemo simulacijo.

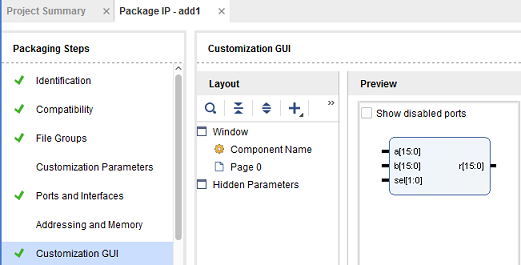

## Pakiranje IP

Orodje **Vivado** omogoča grafično izdelavo digitalnega sistema iz komponent intelektualne lastnine (IP).

Projket z opisom vezja v jeziku VHDL lahko preprosto pretvorimo (zapakiramo) v komponento IP z izbiro

iz menuja *Tools > Create and Package NEW IP*, klikni *Next* in izbiro *Package your current project*.

Izdelavo IP sprožimo v zavihku Review and Package s klikom na **Package IP**. Ob privzetih nastavitvah bo

program naredil paket (*.zip) v katerem je:

* opis komponente, nastavitev in vključenih datotek (*.xml),

* izvorna datoteka (*.vhd),

* opis grafičnega simbola (xgui, *.tcl)