[Home](index.html) | [Vivado](vivado.htm) | [Blokovni diagram](vivado-blok.htm) | [Enostaven IP](vivado-ip.htm) | AXI IP

[SDK](sdk.htm)

# Komponenta AXI IP

Predstavili bomo izdelavo sistema s periferno komponento AXI na osnovi vzorčne komponente

iz programa **Vivado**. Naredili bomo nov projket z blokovnim diagramom, izdelali vzorčno komponento AXI IP,

jo postavili na diagram in nato z urejanjem komponente dodali želeno logiko in dokončali sistem.

## Priprava

V programu Vivado 2017 izberi **Create Project**, določi ime, npr. `blok2` in lokacijo `D:/designs/moja_mapa`.

Nato 4-krat klikni Next, da ostanejo privzete opcije, na koncu pa določi **Default Part**

s klikom na gumb Boards in izbiro `ZedBoard Zynq Evaluation and Development Kit`. V nastavitvah

(Settings, Target language) se prepričaj, da je izbran ciljni jezik VHDL.

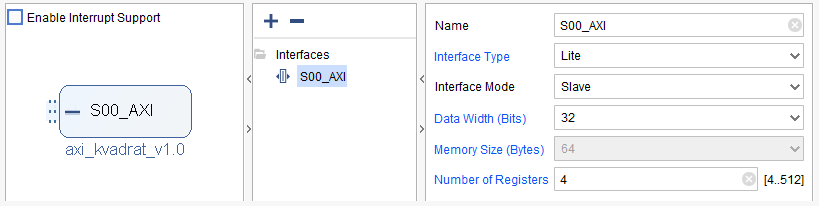

Izberi iz menuja *Tools > Create and Package NEW IP*, klikni *Next* in izberi opcijo

*Create a new AXI4 peripheral*. V naslednjem oknu v polju Name nastavi ime vezja, npr. `axi_kvadrat`

in izberi lokacijo projektne mape (IP location), npr. `D:/designs/DIVS/blok2/ip`

V naslednjem oknu pusti privzeto izbiro nastavitev perifernega vmesnika: AXI Lite s 4 registri.

V zadnjem oknu pustimo privzeto možnost: Add IP to the repository. Z izbiro Edit IP pa bi takoj

odprli nov projekt za urejanje komponente pred pakiranjem.

## Blokovni diagram

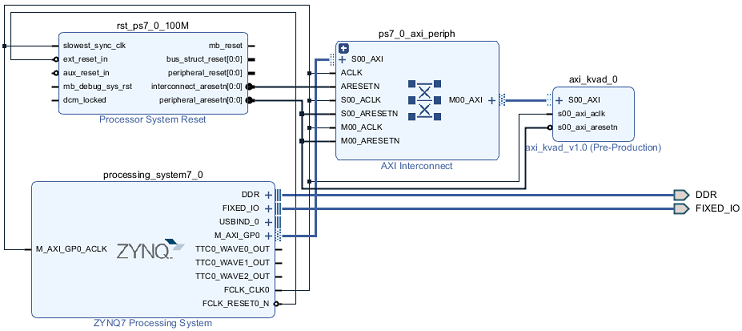

V meniju na levi klikni **Create Block Design**, da se odpre novo okno za risanje blokovnega diagrama.

Klikni na Add IP (ikona + ali ctrl+i), v polje Search zapiši `Zynq` in izberi `ZYNQ7 Processing System`.

S klikom na **Run Block Automation** naredi zunanje povezave procesorja (DDR in FIXED IO).

Dodaj v diagram še novo komponento AXI: Add IP in v Search vnesi `kvad`, nato pa klikni na

**Run Connection Automation**, da bo program dodal AXI Interconnect in Processor System Reset ter

naredil ustrezne povezave.

## Urejanje in ponovno pakiranje komponente IP

Logiko komponente IP iz blokovnega diagrama uredimo tako, da z desnim klikom na komponento izberemo

Edit IP in Packager in potrdimo lokacijo začasnega projekta. S tem korakom odpremo nov projekt v

programu **Vivado**, kjer lahko urejamo VHDL kodo v Design Sources.

V periferno enoto s štirimi registri bomo dodali logiko, ki izračuna kvadrat vrednosti iz prvega registra.

Opis komponente AXI IP je v datoteki: axi_kvadrat_v1_0.vhd, v kateri je vključena axi_kvadrat_v1_0_S00_AXI.vhd.

Z dvoklikom na ime datoteke v Design Sources odpri axi_kvadrat_v1_0_S00_AXI in dodaj deklaracijo dveh

signalov v arhitekturni stavek:

```vhdl

architecture arch_imp of axi_kvadrat_v1_0_S00_AXI is

signal x: unsigned(15 downto 0);

signal y: unsigned(31 downto 0);

```

Predzadnji proces v opisu vezja predstavlja dekodiranje naslovov in branje registrov.

V tem procesu zamenjaj register slv_reg0 s signalom y, ki ga je potrebno pretvoriti v std_logic_vector.

```vhdl

-- Address decoding for reading registers

loc_addr := axi_araddr(ADDR_LSB + OPT_MEM_ADDR_BITS downto ADDR_LSB);

case loc_addr is

when b"00" =>

reg_data_out <= std_logic_vector(y); -- namesto slv_reg0

when b"01" =>

reg_data_out <= slv_reg1;

```

Na koncu dodaj še logiko, ki poveže signal x s prvim registrom (uporabimo le 16 bitov) in izračuna kvadrat:

```vhdl

-- Add user logic here

x <= unsigned(slv_reg0(15 downto 0));

y <= x * x;

-- User logic ends

```

end arch_imp;

Ko naredimo spremembe, odpremo zavihek Package IP, izberemo korak File Groups in potrdimo

Merge changes from File Groups Wizard. Nato izberemo korak Review and Package in kliknemo **Re-Package IP**,

ki ponovno zapakira komponento in zapre začasni projekt.

## Izdelava sistema

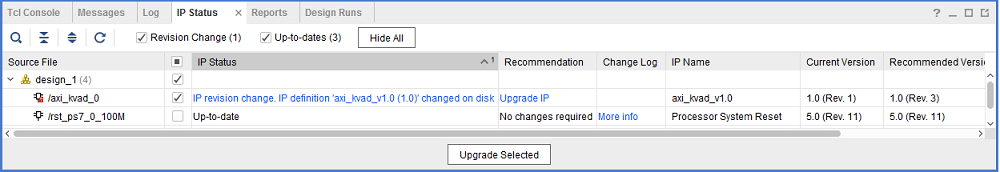

Ko se vrnemo na projekt z blokovnim diagramom, moramo najprej osvežiti komponento. Izberemo iz menuja

Tools > Report > Report IP Status, da se na spodnjem oknu odpre zavihek IP Status, ki zahteva nadgradnjo

spremenjene komponente.

Nadgradnjo potrdimo s klikom na gumb **Upgrade Selected**, ki takoj nato odpre

novo okno, kjer kliknemo **Generate**. Nato zaključi opis sistema: izberi zavihek *Hierarchy*

in v *Design Sources* z desnim gumbom klikni na datoteko diagrama design_1,

izberi **Create HDL Wrapper** ter potrdi privzeto izbiro (Let Vivado manage...).

## Testni program

```C

#include <stdio.h>

#include "xparameters.h"

#include "xil_io.h"

int main()

{

int y;

Xil_Out32(XPAR_AXI_KVADRAT_0_S00_AXI_BASEADDR, 5); // nastavi x = 5

y = Xil_In32(XPAR_AXI_KVADRAT_0_S00_AXI_BASEADDR); // beri y = x*x

return 0;

}

```