Navodila za visokonivojsko modeliranje logike

Modeliranje in simulacija v treh korakih

1. Signali in model vezja

1. Signali in model vezja

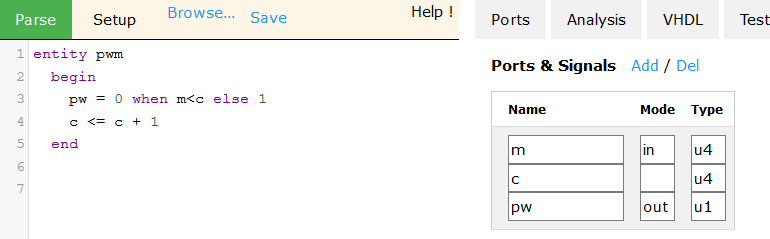

Model digitalnega vezja opišemo v poenostavljenem strojno opisnem jeziku SHDL. Model vezja sestavlja: ime entitete, deklaracija signalov in blok stavkov med begin in end. Primer modela 4-bitnega števca z omogočanjem štetja (en):

entity stevec

en: in u1

st: out u4

begin

if (en) then

st <= st + 1

end

end

- Signali vrste in so vhodi, out so izhodi, za notranje signale pa pustimo prazno polje.

- Tip določa črka u (unsigned) ali s (signed) in število bitov, ki je med 1 in 64.

- Primer: u1 - enobitni, u4 - 4-bitni nepredznačen in s8 je 8-bitni predznačen signal.

Opis vezja naredimo s prireditvenimi in pogojnimi stavki v poenostavljeni sintaksi jezika VHDL. Izvajajo se paralelno (sočasno), ker predstavljajo opis delov vezja.

- Blok stavkov je zaporedje stavkov, ki so vsak v svoji vrstici ali pa ločeni s podpičjem.

- Prireditveni stavki z operatorjem

=se izvedejo takoj (kombinacijsko), z operatorjem<=pa ob fronti ure (sekvenčno). - Pogojni stavek v katerem je en sam stavek zapišemo kompaktno: "if (pogoj) stavek",

če mu sledi blok več stavkov pa v obliki: "if pogoj then blok stavkov end".

Pogojni stavek pozna tudi else in elsif za zaporedne pogoje, kot v jeziku VHDL. - Znotraj bloka lahko le enkrat priredimo vrednost posameznemu signalu!

- Vrstni red prireditev različnim signalom znoraj bloka ni pomemben.

2. Prevajanje

Prevajanje modela izvedemo s klikom na gumb Parse . Prevajalnik bo pod opisom vezja javil uspešen zaključek (Parse finished.) ali pa sporočil napako. Sporočilo o napaki vsebuje kratek opis in mesto. Primer: Napaka v 1:8: Pričakujem ')'! sporoča, da smo v prvi vrstici na 8 mestu verjetno pozabili zaklepaj.

Ko model prevedemo brez napak, dobimo v zavihku Analysis tabelo Resources s seznamom zaznanih gradnikov vezja. Zavihek VHDL prikaže kodo modela vezja v jeziku VHDL. Klik na copy uporabimo za enostaven prenos opisa v odložišče in nato v programsko opremo za simulacijo in sintezo logike iz jezika VHDL.

3. Simulacija

Simulacijo izvedemo tako, da v oknu s signali nastavimo vrednosti vhodov in izvedemo Run . Vrednost enobitnih signalov nastavljamo z levim klikom na posamezen cikel ali potegom čez več ciklov, vrednost vektorja pa se nastavi ob kliku glede na vpisano vrednost okenca Value. Če kliknemo na ime signala se odpre pogovorno okno za nastavitev vrednosti v vseh ciklih, z desnim klikom na signal pa preklapljamo med desetiškim, dvojiškim in analognim prikazom. Število simulacijskih ciklov nastavimo v okencu Cycles in ob spremembi ponovno prevedemo vezje.