## Introduction

- Set of techniques used in digital circuit verification, test development, design debug and diagnosis.

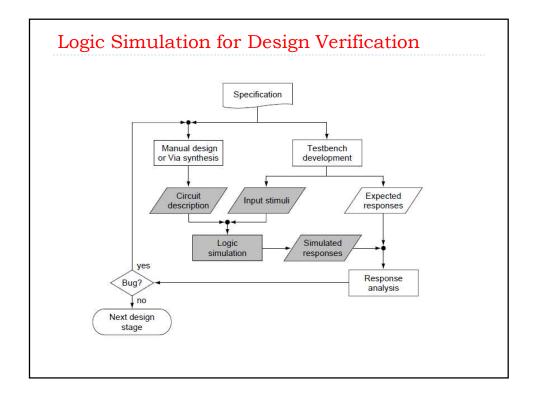

- Simulation is the process of predicting the behaviour of the circuit design before the circuit is fabricated.

- In digital circuits, simulation has two purposes:

- To verify whether the design meets its functional specification and contains any design errors. This process is referred to as logic simulation or fault-free simulation. This process is called also verification.

- In test development proces, fault simulation is used to simulate the faulty circuit.

- Faulty circuit is simulated with a set of test patterns that help to locate/diagnose any manufacturing defects.

- Fault simulation is also important component of ATPG programs.

• Each FF should have unique unknown symbol  $u_i$

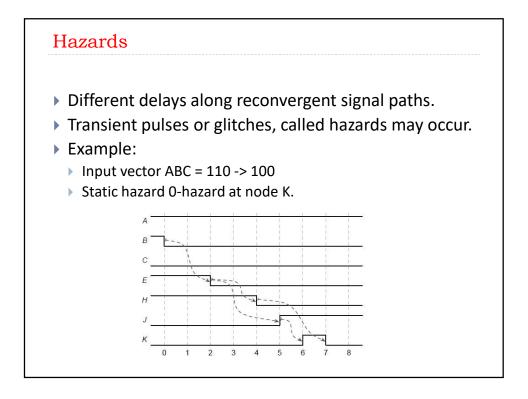

| Types of H                                                                         | azards                                |                                       |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|--|--|--|--|--|--|--|

|                                                                                    | e: static and dy<br>rds are static 1- | namic.<br>hazard and static 0-hazard. |  |  |  |  |  |  |  |

|                                                                                    | static 1-hazard                       | static 0-hazard                       |  |  |  |  |  |  |  |

| <ul> <li>Dynamic hazards are dynamic 1-hazard and dynamic<br/>0-hazard.</li> </ul> |                                       |                                       |  |  |  |  |  |  |  |

|                                                                                    | dynamic 1-hazard                      | dynamic 0-hazard                      |  |  |  |  |  |  |  |

|                                                                                    |                                       |                                       |  |  |  |  |  |  |  |

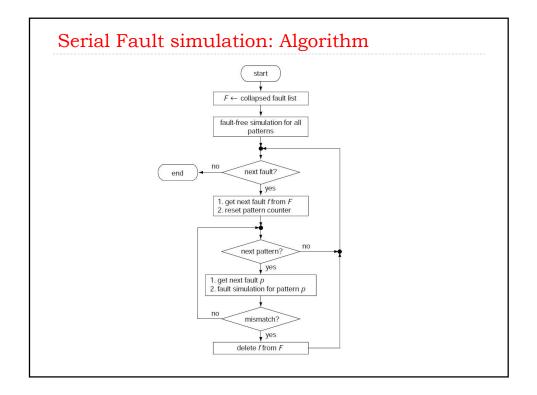

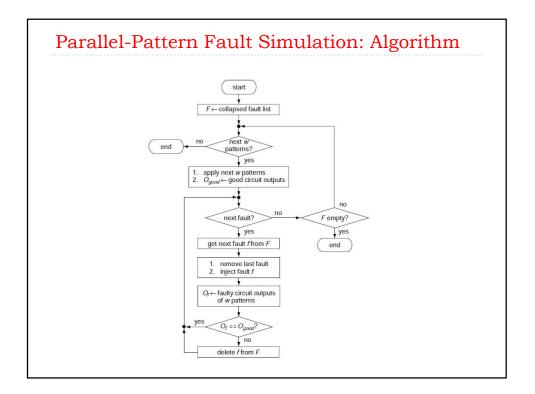

- The simplest fault simulation technique.

- It consists of

- fault-free and

- faulty circuit simulations.

- The fault-free responses are stored to determine later whether a test pattern can detect a fault or not.

- > Serial fault simulation simulates faults one at a time.

- > Presence of the fault is done with a **fault injection**.

- The faulty circuit is then simulated with a given test pattern to derive the faulty response.

- The process repeats until all faults in the fault list are simulated (fault dropping).

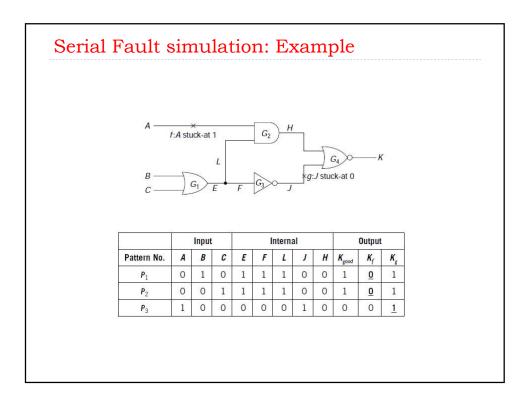

|                       |    | Input    |                |   |   | Internal |   |     |   |                       |            | Output   |  |  |

|-----------------------|----|----------|----------------|---|---|----------|---|-----|---|-----------------------|------------|----------|--|--|

|                       |    | A        | A <sub>f</sub> | В | С | Ε        | F | L   | J | <b>J</b> <sub>g</sub> | Н          | K        |  |  |

|                       | FF | 0        | $\bigcirc$     | 1 | 0 | 1        | 1 | (1) | 0 | 0                     | $\bigcirc$ | 1        |  |  |

| $P_1$                 | f  | <u>0</u> | 1              | 1 | 0 | 1        | 1 | 1   | 0 | 0                     | 1          | <u>0</u> |  |  |

|                       | g  | 0        | 0              | 1 | 0 | 1        | 1 | 1   | 0 | 0                     | 6          | 1        |  |  |

|                       | FF | 0        | 0              | 0 | 1 | 1        | 1 | 1   | 0 | 0                     | 0          | 1        |  |  |

| <b>P</b> <sub>2</sub> | f  | 0        | 1              | 0 | 1 | 1        | 1 | 1   | 0 | 0                     | 1          | <u>0</u> |  |  |

|                       | g  | 0        | 0              | 0 | 1 | 1        | 1 | 1   | 0 | 0                     | 0          | 1        |  |  |

|                       | FF | 1        | 1              | 0 | 0 | 0        | 0 | 0   | 1 | 1                     | 0          | 0        |  |  |

| <b>P</b> 3            | f  | 1        | 1              | 0 | 0 | 0        | 0 | 0   | 1 | 1                     | 0          | 0        |  |  |

|                       | g  | 1        | 1              | 0 | 0 | 0        | 0 | 0   | 1 | <u>0</u>              | 0          | <u>1</u> |  |  |

|            | Input                 |                 |   |   | 8 | Output |    |   |                   |          |  |

|------------|-----------------------|-----------------|---|---|---|--------|----|---|-------------------|----------|--|

|            |                       | A               | В | C | E | F      | L  | J | H                 | K        |  |

| Fault-free | <b>P</b> <sub>1</sub> | 0               | 1 | 0 | 1 | 1      | 1  | 0 | 0                 | 1        |  |

|            | <b>P</b> <sub>2</sub> | 0               | 0 | 1 | 1 | 1      | 1  | 0 | 0                 | 1        |  |

|            | <b>P</b> <sub>3</sub> | 1               | 0 | 0 | 0 | 0      | 0  | 1 | 0                 | 0        |  |

| f          | <b>P</b> <sub>1</sub> | $\underline{1}$ | 1 | 0 | 1 | 1      | 1  | 0 | $(\underline{1})$ | <u>0</u> |  |

|            | <b>P</b> <sub>2</sub> | 1               | 0 | 1 | 1 | 1      | 1  | 0 | 1                 | <u>0</u> |  |

|            | <b>P</b> <sub>3</sub> | V               | 0 | 0 | 0 | 0      | 0/ | 1 | 0/                | 0        |  |

| g          | <b>P</b> <sub>1</sub> | 0               | 1 | 0 | 1 | 1      | 1  | 0 | 0                 | 1        |  |

|            | <b>P</b> <sub>2</sub> | 0               | 0 | 1 | 1 | 1      | 1  | 0 | 0                 | 1        |  |

|            | <b>P</b> <sub>3</sub> | 1               | 0 | 0 | 0 | 0      | 0  | 0 | 0                 | <u>1</u> |  |

## Other methods for fault simulation

- Concurrent fault simulation

- Differential fault simulation

- Fault sampling

- Statistical fault analysis

- And several others ...

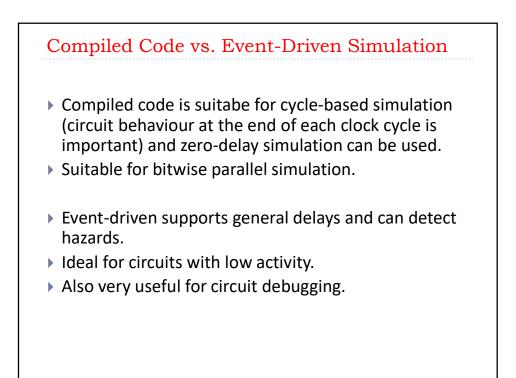

## Conclusion Logic simulation Checks whether the design will behave as predicted before its physical implementation. Event-driven simulation technique is most widely used today. Fault simulation We have information in advance how effective is the given test pattern set in detecting faults. Logic and fault simulation programs are part of every commercial tool for circuit design !!