DESIGN FOR **TESTABILITY**  PRINCIPLES AND ARCHITECTURES

#### In Praise of VLSI Test Principles and Architectures: Design for Testability

Testing techniques for VLSI circuits are today facing many exciting and complex challenges. In the era of large systems embedded in a single system-on-chip (SOC) and fabricated in continuously shrinking technologies, it is important to ensure correct behavior of the whole system. Electronic design and test engineers of today have to deal with these complex and heterogeneous systems (digital, mixed-signal, memory), but few have the possibility to study the whole field in a detailed and deep way. This book provides an extremely broad knowledge of the discipline, covering the fundamentals in detail, as well as the most recent and advanced concepts.

It is a textbook for teaching the basics of fault simulation, ATPG, memory testing, DFT and BIST. However, it is also a complete testability guide for an engineer who wants to learn the latest advances in DFT for soft error protection, logic built-in self-test (BIST) for at-speed testing, DRAM BIST, test compression, MEMS testing, FPGA testing, RF testing, etc.

**Michel Renovell**, Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM), Montpellier, France

This book combines in a unique way insight into industry practices commonly found in commercial DFT tools but not discussed in textbooks, and a sound treatment of the technical fundamentals. The comprehensive review of future test technology trends, including self-repair, soft error protection, MEMS testing, and RF testing, leads students and researchers to advanced DFT research.

#### Hans-Joachim Wunderlich, University of Stuttgart, Germany

Recent advances in semiconductor manufacturing have made design for testability (DFT) an essential part of nanometer designs. The lack of an up-to-date DFT textbook that covers the most recent DFT techniques, such as at-speed scan testing, logic built-in self-test (BIST), test compression, memory built-in self-repair (BISR), and future test technology trends, has created problems for students, instructors, researchers, and practitioners who need to master modern DFT technologies. I am pleased to find a DFT textbook of this comprehensiveness that can serve both academic and professional needs.

Andre Ivanov, University of British Columbia, Canada

This is the most recent book covering all aspects of digital systems testing. It is a "must read" for anyone focused on learning modern test issues, test research, and test practices.

#### Kewal K. Saluja, University of Wisconsin-Madison

Design for testability (DFT) can no longer be considered as a graduate-level course. With growing design starts worldwide, DFT must be also part of the undergraduate curriculum. The book's focus on VLSI test principles and DFT architectures, while deemphasizing test algorithms, is an ideal choice for undergraduate education. In addition, system-on-chip (SOC) testing is one among the most important technologies for the development of ultra-large-scale integration (ULSI) devices in the 21st century. By covering the basic DFT theory and methodology on digital, memory, as well as analog and mixed-signal (AMS) testing, this book further stands out as one best reference book that equips practitioners with testable SOC design skills.

# VLSI TEST PRINCIPLES AND ARCHITECTURES

#### The Morgan Kaufmann Series in Systems on Silicon

Series Editor: Wayne Wolf, Princeton University

The rapid growth of silicon technology and the demands of applications are increasingly forcing electronics designers to take a systems-oriented approach to design. This has led to new challenges in design methodology, design automation, manufacture and test. The main challenges are to enhance designer productivity and to achieve correctness on the first pass. *The Morgan Kaufmann Series in Systems on Silicon* presents high-quality, peer-reviewed books authored by leading experts in the field who are uniquely qualified to address these issues.

The Designer's Guide to VHDL, Second Edition

Peter J. Ashenden

The System Designer's Guide to VHDL-AMS

Peter J. Ashenden, Gregory D. Peterson, and Darrell A. Teegarden

Readings in Hardware/Software Co-Design

Edited by Giovanni De Micheli, Rolf Ernst, and Wayne Wolf

Modeling Embedded Systems and SoCs

Axel Jantsch

ASIC and FPGA Verification: A Guide to Component Modeling

Richard Munden

Multiprocessor Systems-on-Chips

Edited by Ahmed Amine Jerraya and Wayne Wolf

Comprehensive Functional Verification

Bruce Wile, John Goss, and Wolfgang Roesner

Customizable Embedded Processors: Design Technologies and Applications

Edited by Paolo Ienne and Rainer Leupers

Networks on Chips: Technology and Tools Giovanni De Micheli and Luca Benini

Designing SOCs with Configured Cores: Unleashing the Tensilica Diamond Cores

Steve Leibson

VLSI Test Principles and Architectures: Design for Testability

Edited by Laung-Terng Wang, Cheng-Wen Wu, and Xiaoqing Wen

#### **Contact Information**

Charles B. Glaser

Senior Acquisitions Editor

Elsevier

(Morgan Kaufmann; Academic Press; Newnes)

(781) 313-4732

c.glaser@elsevier.com

http://www.books.elsevier.com

Wayne Wolf

Professor

Electrical Engineering, Princeton University

(609) 258-1424

wolf@princeton.edu

http://www.ee.princeton.edu/~wolf/

# VLSI TEST PRINCIPLES AND ARCHITECTURES DESIGN FOR TESTABILITY

Edited by

Laung-Terng Wang Cheng-Wen Wu Xiaoqing Wen

Acquisitions Editor Charles B. Glaser

Publishing Services Manager George Morrison

Production Editor Dawnmarie Simpson

Assistant Editor Michele Cronin

Production Assistant Melinda Ritchie

Cover Design Paul Hodgson

Cover Illustration ©Dennis Harms/Getty Images

Composition Integra Software Services

Technical Illustration Integra Software Services

Copyeditor Sarah Fortener

Proofreader Phyllis Coyne et al. Proofreading Services

Indexer Broccoli Information Management

Interior printer The Maple-Vail Book Manufacturing Group

Cover printer Phoenix Color Corporation

Morgan Kaufmann Publishers is an imprint of Elsevier. 500 Sansome Street. Suite 400. San Francisco. CA 94111

This book is printed on acid-free paper.

© 2006 by Elsevier Inc. All rights reserved.

Designations used by companies to distinguish their products are often claimed as trademarks or registered trademarks. In all instances in which Morgan Kaufmann Publishers is aware of a claim, the product names appear in initial capital or all capital letters. Readers, however, should contact the appropriate companies for more complete information regarding trademarks and registration.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopying, scanning, or otherwise—without prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, E-mail: permissions@elsevier.com. You may also complete your request online via the Elsevier homepage (http://elsevier.com), by selecting "Support & Contact" then "Copyright and Permission" and then "Obtaining Permissions."

#### Library of Congress Cataloging-in-Publication Data

VLSI test principles and architectures: design for testability/edited by

Laung-Terng Wang, Cheng-Wen Wu, Xiaoqing Wen.

p. cm.

Includes bibliographical references and index.

ISBN-13: 978-0-12-370597-6 (hardcover: alk. paper)

ISBN-10: 0-12-370597-5 (hardcover: alk. paper)

- $1. \ \ \, Integrated\ circuits\\ -- Very\ large\ scale\ integration\\ -- Testing. \\ scale\ integration\\ -- Design.$

- I. Wang, Laung-Terng. II. Wu, Cheng-Wen, EE Ph.D. III. Wen, Xiaoqing.

TK7874.75.V587 2006

621.39'5—dc22

2006006869

2. Integrated circuits-Very large

ISBN 13: 978-0-12-370597-6 ISBN 10: 0-12-370597-5

For information on all Morgan Kaufmann publications, visit our Web site at www.mkp.com or www.books.elsevier.com

Printed in the United States of America

06 07 08 09 10 5 4 3 2 1

# Working together to grow libraries in developing countries

www.elsevier.com | www.bookaid.org | www.sabre.org

ELSEVIER

BOOK AID International

Sabre Foundation

### **CONTENTS**

| Pı | reface  | •                                          |                                                                                                                                                               |                                                                                                                                                                                                                                                  |          | xxi                                                                           |

|----|---------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------|

| In | the (   | Classro                                    | om                                                                                                                                                            |                                                                                                                                                                                                                                                  | X        | xiv                                                                           |

| A  | cknov   | vledgn                                     | nents                                                                                                                                                         |                                                                                                                                                                                                                                                  |          | xxv                                                                           |

| C  | ontrib  | outors                                     |                                                                                                                                                               |                                                                                                                                                                                                                                                  | X        | xvii                                                                          |

| Al | bout 1  | the Edi                                    | itors                                                                                                                                                         |                                                                                                                                                                                                                                                  | X        | xix                                                                           |

| 1  | Intr    | oduct                                      | ion                                                                                                                                                           |                                                                                                                                                                                                                                                  |          | 1                                                                             |

|    | Ying    | hua Min                                    | and Charle                                                                                                                                                    | es Stroud                                                                                                                                                                                                                                        |          |                                                                               |

|    | 1.1 1.2 | Testin<br>1.2.1<br>1.2.2<br>1.2.3          | g During to<br>VLSI De<br>1.2.1.1<br>1.2.1.2<br>Electron<br>System-Inges in VI<br>Test Ger<br>Fault Mo<br>1.3.2.1<br>1.3.2.2<br>1.3.2.3<br>1.3.2.4<br>1.3.2.5 | he VLSI Lifecycle velopment Process Design Verification Yield and Reject Rate ic System Manufacturing Process Level Operation SI Testing heration odels Stuck-At Faults Transistor Faults Open and Short Faults Delay Faults and Coupling Faults |          | 1<br>2<br>3<br>4<br>5<br>6<br>6<br>8<br>9<br>11<br>12<br>15<br>16<br>19<br>20 |

|    | 1.4     | Levels<br>1.4.1<br>1.4.2<br>1.4.3<br>1.4.4 | Register<br>Gate Lev<br>Switch I                                                                                                                              | Analog Fault Models                                                                                                                                                                                                                              | <br><br> | 21<br>22<br>22<br>23<br>24<br>24                                              |

viii Contents

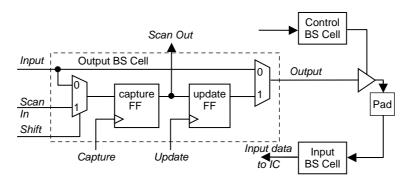

|   | 1.5             | Histor<br>1.5.1<br>1.5.2<br>1.5.3<br>1.5.4<br>1.5.5<br>1.5.6<br>1.5.7 | Automat:<br>Automat:<br>Fault Sin<br>Digital C<br>Analog a<br>Design fo | v of VLSI Test Technology                   | . 25<br>. 27<br>. 28<br>. 28<br>. 29<br>. 29 |

|---|-----------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------|

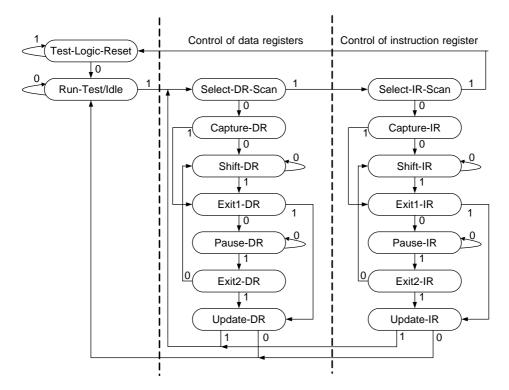

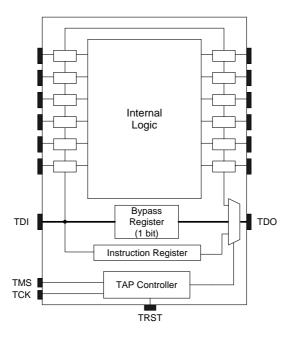

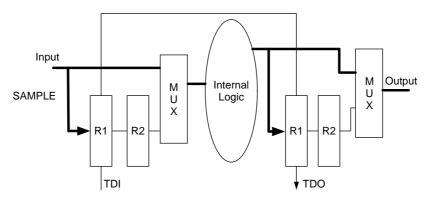

|   | 4 /             | 1.5.8                                                                 | Boundar                                                                 | y Scan Testing                              | . 32                                         |

|   | 1.6             |                                                                       | _                                                                       | arks                                        |                                              |

|   | 1.7             |                                                                       |                                                                         |                                             |                                              |

|   |                 | _                                                                     |                                                                         |                                             |                                              |

|   | Kelei           | ences .                                                               |                                                                         |                                             | . 34                                         |

| 2 | Des             | ign fo                                                                | r Testabi                                                               | ility                                       | 37                                           |

|   | 7               | T                                                                     | (I T ) III                                                              | Vine vive W 1 VI - 1 C Al. 1.1 II - f -     |                                              |

|   |                 | 0 0                                                                   |                                                                         | ng, Xiaoqing Wen, and Khader S. Abdel-Hafez | 27                                           |

|   | 2.1             |                                                                       |                                                                         |                                             |                                              |

|   | 2.2             |                                                                       |                                                                         | sis                                         |                                              |

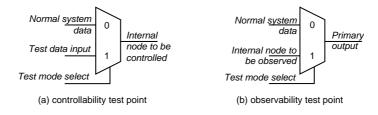

|   |                 | 2.2.1                                                                 | 2.2.1.1                                                                 | Testability Analysis                        | . 41                                         |

|   |                 |                                                                       | 2.2.1.1                                                                 | Combinational Controllability and           | 41                                           |

|   |                 |                                                                       | 2212                                                                    | Observability Calculation                   | . 41                                         |

|   |                 |                                                                       | 2.2.1.2                                                                 | Sequential Controllability and              | . 43                                         |

|   |                 | 222                                                                   | Dualaalaili                                                             | Observability Calculation                   |                                              |

|   |                 | 2.2.2<br>2.2.3                                                        |                                                                         | ity-Based Testability Analysis              |                                              |

|   |                 | 2.2.3                                                                 |                                                                         | on-Based Testability Analysis               |                                              |

|   | 2.3             |                                                                       |                                                                         | tability Analysis                           |                                              |

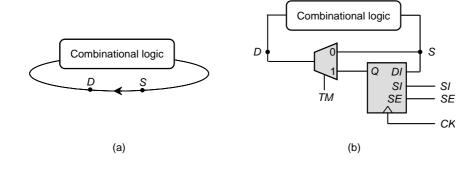

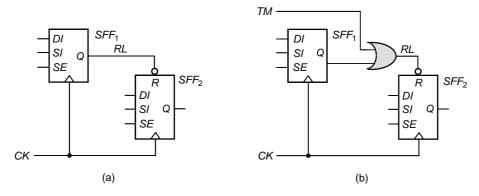

|   | 2.3             | 2.3.1                                                                 |                                                                         | pility Basics                               |                                              |

|   |                 | 2.3.1                                                                 | 2.3.1.1                                                                 | Approach                                    |                                              |

|   |                 | 2.3.2                                                                 |                                                                         | Test Point Insertion                        |                                              |

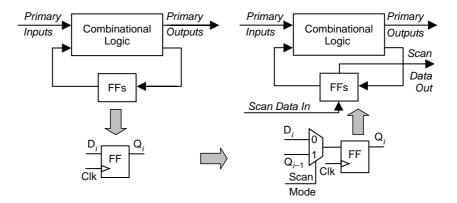

|   | 2.4             |                                                                       |                                                                         | ed Approach                                 |                                              |

|   | 2. <del>4</del> | 2.4.1                                                                 |                                                                         | s                                           |                                              |

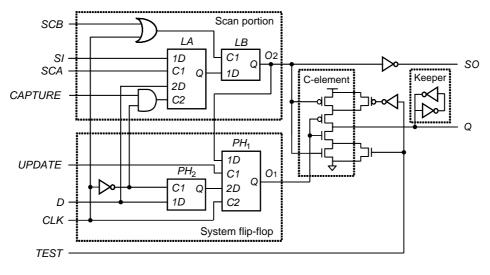

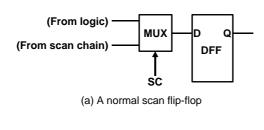

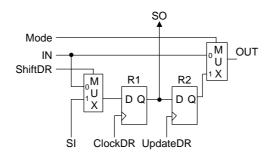

|   |                 | 2.4.1                                                                 |                                                                         | Scan Cell                                   |                                              |

|   |                 | 2.4.3                                                                 |                                                                         | an Cell                                     |                                              |

|   | 2.5             |                                                                       |                                                                         | es                                          |                                              |

|   | 2.5             | 2.5.1                                                                 |                                                                         | n Design                                    |                                              |

|   |                 | 2.3.1                                                                 | 2.5.1.1                                                                 | Muxed-D Full-Scan Design                    |                                              |

|   |                 |                                                                       | 2.5.1.1                                                                 | Clocked Full-Scan Design                    |                                              |

|   |                 |                                                                       | 2.5.1.2                                                                 | LSSD Full-Scan Design                       |                                              |

|   |                 | 2.5.2                                                                 |                                                                         | can Design                                  |                                              |

|   |                 | 2.5.2                                                                 |                                                                         | -Access Scan Design                         |                                              |

|   | 2.6             |                                                                       |                                                                         | es                                          |                                              |

|   | 2.0             | 2.6.1                                                                 | _                                                                       | Buses                                       |                                              |

|   |                 | 2.6.1                                                                 |                                                                         | onal I/O Ports                              | 71                                           |

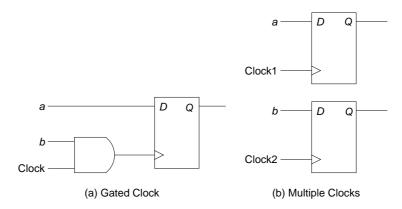

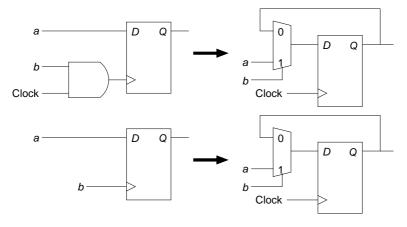

|   |       | 2.6.3   | Gated Clocks                                   |      |      |       | 71  |

|---|-------|---------|------------------------------------------------|------|------|-------|-----|

|   |       | 2.6.4   | Derived Clocks                                 |      |      |       | 74  |

|   |       | 2.6.5   | Combinational Feedback Loops                   |      |      |       | 74  |

|   |       | 2.6.6   | Asynchronous Set/Reset Signals                 |      |      |       | 75  |

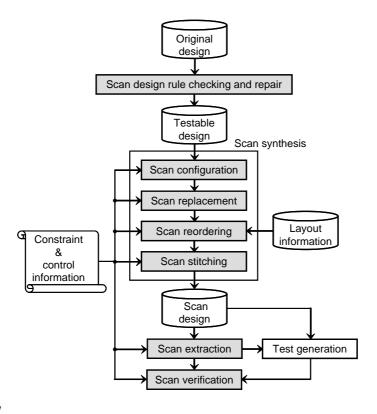

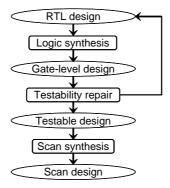

|   | 2.7   | Scan D  | esign Flow                                     |      |      |       | 76  |

|   |       | 2.7.1   | Scan Design Rule Checking and Repair           |      |      |       | 77  |

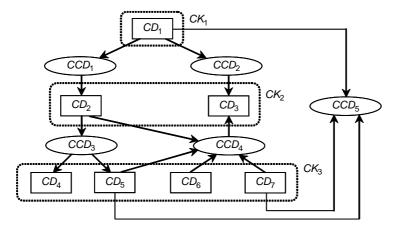

|   |       | 2.7.2   | Scan Synthesis                                 |      |      |       | 78  |

|   |       |         | 2.7.2.1 Scan Configuration                     |      |      |       | 79  |

|   |       |         | 2.7.2.2 Scan Replacement                       |      |      |       | 82  |

|   |       |         | 2.7.2.3 Scan Reordering                        |      |      |       | 82  |

|   |       |         | 2.7.2.4 Scan Stitching                         |      |      |       | 83  |

|   |       | 2.7.3   | Scan Extraction                                |      |      |       | 83  |

|   |       | 2.7.4   | Scan Verification                              |      |      |       | 84  |

|   |       |         | 2.7.4.1 Verifying the Scan Shift Operation     |      |      |       | 85  |

|   |       |         | 2.7.4.2 Verifying the Scan Capture Operation   |      |      |       | 86  |

|   |       | 2.7.5   | Scan Design Costs                              |      |      |       | 86  |

|   | 2.8   | Special | -Purpose Scan Designs                          |      |      |       | 87  |

|   |       | 2.8.1   | Enhanced Scan                                  |      |      |       | 87  |

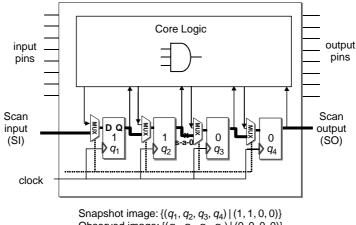

|   |       | 2.8.2   | Snapshot Scan                                  |      |      |       | 88  |

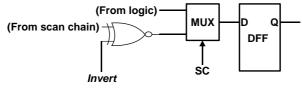

|   |       | 2.8.3   | Error-Resilient Scan                           |      |      |       | 90  |

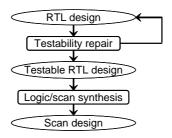

|   | 2.9   | RTL De  | esign for Testability                          |      |      |       | 92  |

|   |       | 2.9.1   | RTL Scan Design Rule Checking and Repair       |      |      |       | 93  |

|   |       | 2.9.2   | RTL Scan Synthesis                             |      |      |       | 94  |

|   |       | 2.9.3   | RTL Scan Extraction and Scan Verification      |      |      |       | 95  |

|   | 2.10  | Conclu  | ding Remarks                                   |      |      |       | 95  |

|   | 2.11  |         | ses                                            |      |      |       | 96  |

|   | Ackno | owledgm | nents                                          |      |      |       | 99  |

|   |       |         |                                                |      |      |       | 99  |

|   |       |         |                                                |      |      |       |     |

| 3 | Log   | ic and  | Fault Simulation                               |      |      | 1     | 05  |

|   |       |         |                                                | <br> | <br> | <br>_ | _   |

|   | Jiun- | Lang Hu | ang, James CM. Li, and Duncan M. (Hank) Walker |      |      |       |     |

|   | 3.1   | Introdu | ıction                                         |      |      |       | 106 |

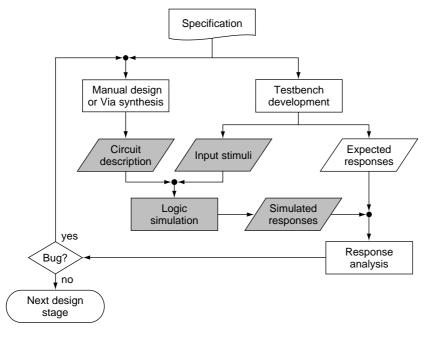

|   |       | 3.1.1   | Logic Simulation for Design Verification       |      |      |       | 106 |

|   |       | 3.1.2   | Fault Simulation for Test and Diagnosis        |      |      |       | 107 |

|   | 3.2   | Simula  | tion Models                                    |      |      |       | 108 |

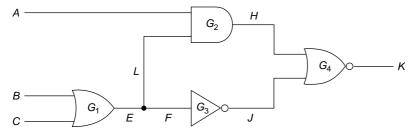

|   |       | 3.2.1   | Gate-Level Network                             |      |      |       | 109 |

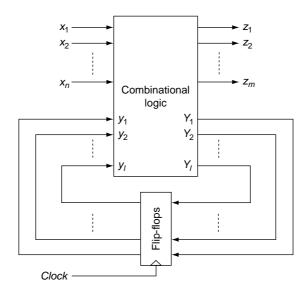

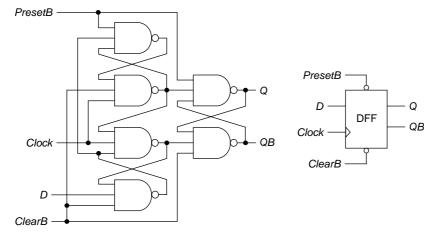

|   |       |         | 3.2.1.1 Sequential Circuits                    |      |      |       | 109 |

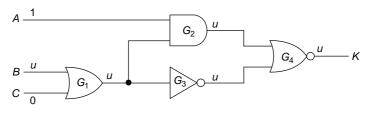

|   |       | 3.2.2   | Logic Symbols                                  |      |      |       |     |

|   |       |         | 3.2.2.1 Unknown State $u \dots \dots \dots$    |      |      |       |     |

|   |       |         | 3.2.2.2 High-Impedance State $Z$               |      |      |       |     |

|   |       |         | 3.2.2.3 Intermediate Logic States              |      |      |       |     |

|   |       | 3.2.3   | Logic Element Evaluation                       |      |      |       |     |

|   |       |         | 3.2.3.1 Truth Tables                           |      |      |       |     |

|   |       |         | 3.2.3.2 Input Scanning                         |      |      |       |     |

Contents

iх

|   |       |           | 3.2.3.3    | Input Counting                          |  |  |     |

|---|-------|-----------|------------|-----------------------------------------|--|--|-----|

|   |       |           | 3.2.3.4    | Parallel Gate Evaluation                |  |  |     |

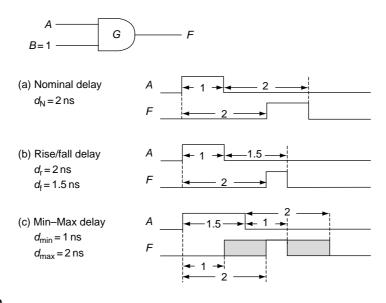

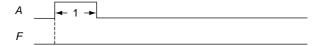

|   |       | 3.2.4     | Timing l   | Models                                  |  |  | 118 |

|   |       |           | 3.2.4.1    | Transport Delay                         |  |  | 118 |

|   |       |           | 3.2.4.2    | Inertial Delay                          |  |  | 119 |

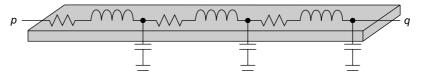

|   |       |           | 3.2.4.3    | Wire Delay                              |  |  | 119 |

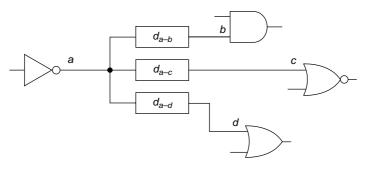

|   |       |           | 3.2.4.4    | Functional Element Delay Model          |  |  | 120 |

|   | 3.3   | Logic S   | Simulation | 1                                       |  |  | 121 |

|   |       | 3.3.1     | Compile    | d-Code Simulation                       |  |  | 121 |

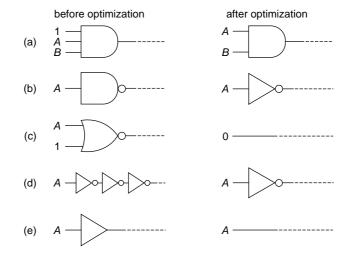

|   |       |           | 3.3.1.1    | Logic Optimization                      |  |  | 121 |

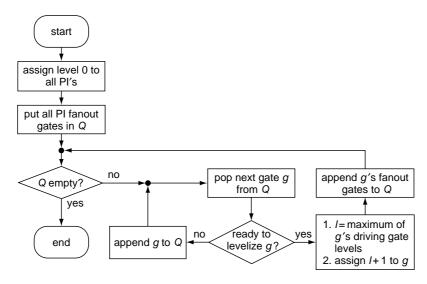

|   |       |           | 3.3.1.2    | Logic Levelization                      |  |  | 123 |

|   |       |           | 3.3.1.3    | Code Generation                         |  |  | 124 |

|   |       | 3.3.2     | Event-D    | riven Simulation                        |  |  | 125 |

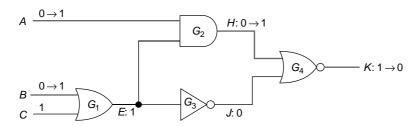

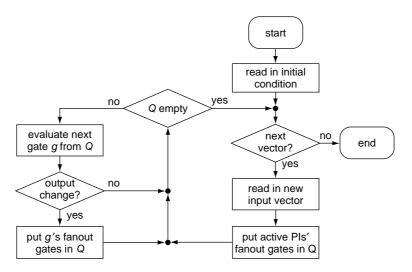

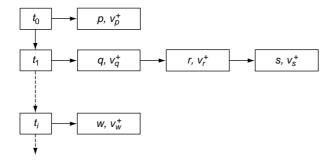

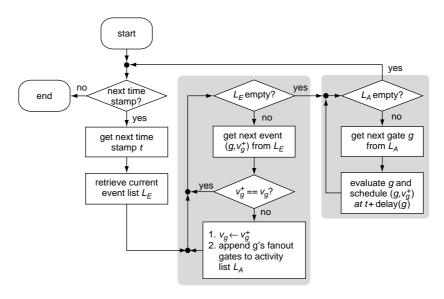

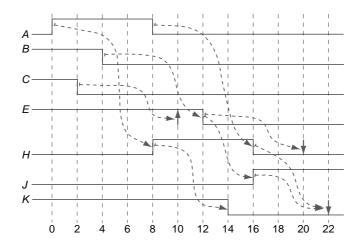

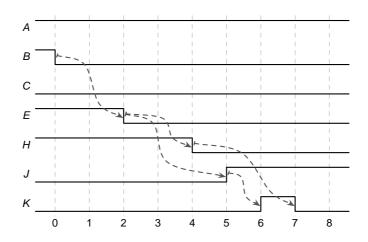

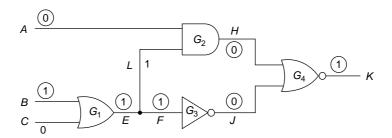

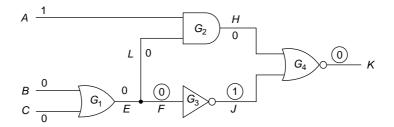

|   |       |           | 3.3.2.1    | Nominal-Delay Event-Driven Simulation   |  |  | 126 |

|   |       | 3.3.3     | Compile    | d-Code Versus Event-Driven Simulation . |  |  |     |

|   |       | 3.3.4     |            |                                         |  |  |     |

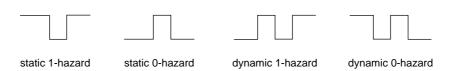

|   |       |           | 3.3.4.1    | Static Hazard Detection                 |  |  |     |

|   |       |           | 3.3.4.2    | Dynamic Hazard Detection                |  |  | 132 |

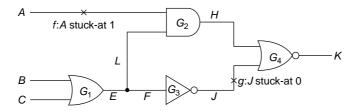

|   | 3.4   | Fault S   | Simulation | 5                                       |  |  |     |

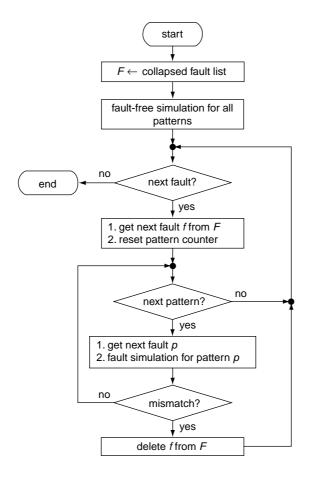

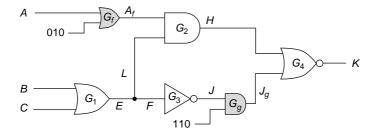

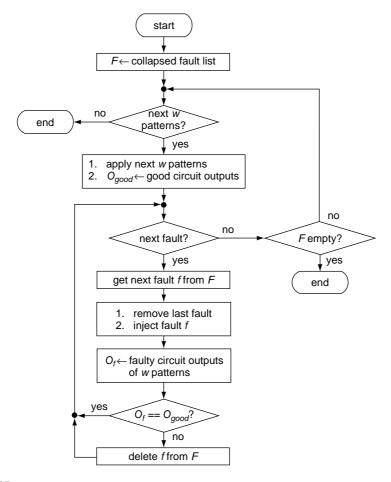

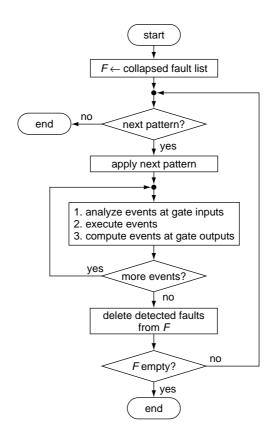

|   |       | 3.4.1     | Serial Fa  | ault Simulation                         |  |  | 133 |

|   |       | 3.4.2     | Parallel   | Fault Simulation                        |  |  | 135 |

|   |       |           | 3.4.2.1    | Parallel Fault Simulation               |  |  | 135 |

|   |       |           | 3.4.2.2    | Parallel-Pattern Fault Simulation       |  |  | 137 |

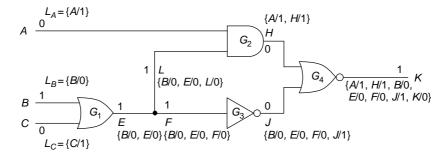

|   |       | 3.4.3     | Deductiv   | re Fault Simulation                     |  |  | 139 |

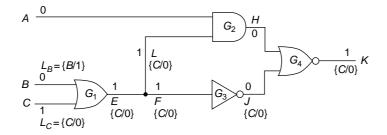

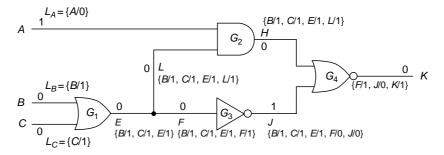

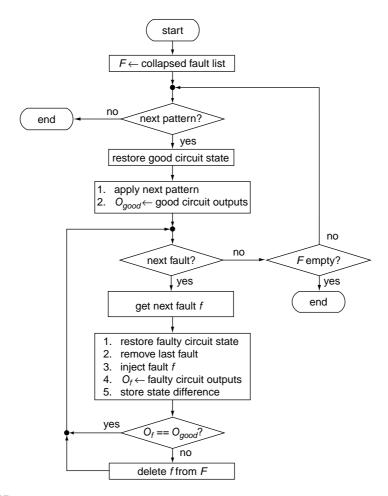

|   |       | 3.4.4     | Concurr    | ent Fault Simulation                    |  |  | 143 |

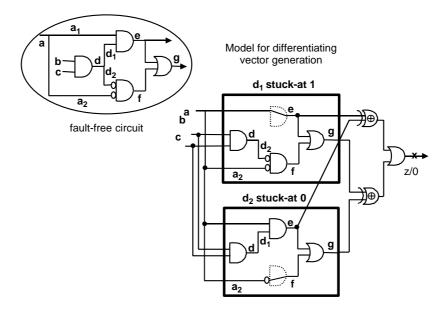

|   |       | 3.4.5     | Differen   | tial Fault Simulation                   |  |  | 146 |

|   |       | 3.4.6     | Fault De   | tection                                 |  |  | 148 |

|   |       | 3.4.7     | Compari    | ison of Fault Simulation Techniques     |  |  | 149 |

|   |       | 3.4.8     | Alternati  | ives to Fault Simulation                |  |  | 151 |

|   |       |           | 3.4.8.1    | Toggle Coverage                         |  |  | 151 |

|   |       |           | 3.4.8.2    | Fault Sampling                          |  |  | 151 |

|   |       |           | 3.4.8.3    | Critical Path Tracing                   |  |  | 152 |

|   |       |           | 3.4.8.4    | Statistical Fault Analysis              |  |  | 153 |

|   | 3.5   | Conclu    | ıding Rem  | arks                                    |  |  | 154 |

|   | 3.6   | Exercis   | ses        |                                         |  |  | 155 |

|   | Refer | ences .   |            |                                         |  |  | 158 |

| 4 | Test  | t Gene    | ration     |                                         |  |  | 161 |

|   | Mich  | ael S. Hs | siao       |                                         |  |  |     |

|   | 4.1   | Introd    | uction     |                                         |  |  | 161 |

|   | 4.2   |           |            | eneration                               |  |  |     |

|   |       | 4.2.1     |            | ive Testing                             |  |  |     |

|   | 4.3   |           |            | ground: Boolean Difference              |  |  |     |

|   |       | 4.3.1     |            | ble Faults                              |  |  |     |

|   |       |           |            |                                         |  |  |     |

| Contents | VI  |

|----------|-----|

| Comemis  | A I |

| 4.4  | Design  | ning a Stuck-At ATPG for Combinational Circuits | 169 |

|------|---------|-------------------------------------------------|-----|

| т.т  | 4.4.1   | A Naive ATPG Algorithm                          |     |

|      | 7.7.1   | 4.4.1.1 Backtracking                            |     |

|      | 4.4.2   | A Basic ATPG Algorithm                          |     |

|      | 4.4.3   | D Algorithm                                     |     |

|      | 4.4.4   | PODEM                                           |     |

|      | 4.4.5   | FAN                                             |     |

|      | 4.4.6   | Static Logic Implications                       |     |

|      | 4.4.7   |                                                 |     |

| 4.5  |         | Dynamic Logic Implications                      |     |

| 4.5  | 4.5.1   | ing a Sequential ATPG                           |     |

|      | 4.5.1   | Time Frame Expansion                            |     |

|      |         | 5-Valued Algebra Is Insufficient                |     |

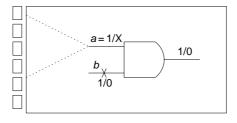

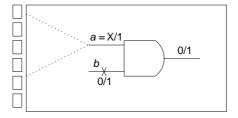

| 1 (  | 4.5.3   | Gated Clocks and Multiple Clocks                |     |

| 4.6  |         | able Fault Identification                       |     |

| 4.7  | 4.6.1   | Multiple-Line Conflict Analysis                 |     |

| 4.7  | _       | ing a Simulation-Based ATPG                     |     |

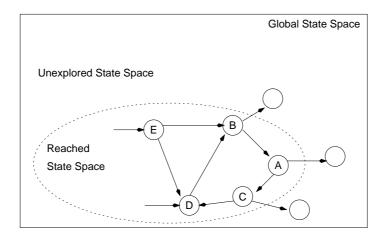

|      | 4.7.1   | Overview                                        |     |

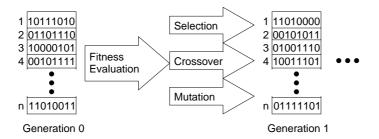

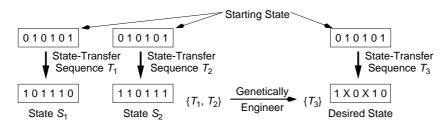

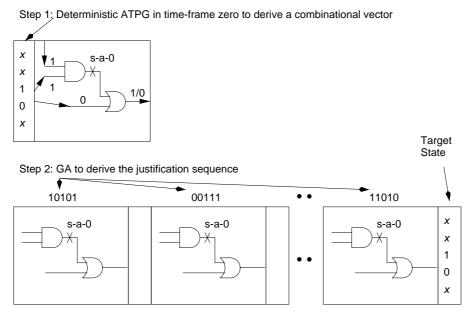

|      | 4.7.2   | Genetic-Algorithm-Based ATPG                    |     |

|      |         | 4.7.2.1 Issues Concerning the GA Population     |     |

|      |         | 4.7.2.2 Issues Concerning GA Parameters         |     |

|      |         | 4.7.2.3 Issues Concerning the Fitness Function  |     |

|      |         | 4.7.2.4 CASE Studies                            |     |

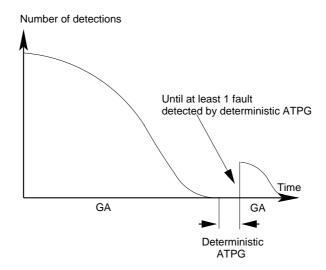

| 4.8  |         | ced Simulation-Based ATPG                       |     |

|      | 4.8.1   | Seeding the GA with Helpful Sequences           |     |

|      | 4.8.2   | Logic-Simulation-Based ATPG                     |     |

|      | 4.8.3   | Spectrum-Based ATPG                             |     |

| 4.9  | U       | d Deterministic and Simulation-Based ATPG       |     |

|      | 4.9.1   | ALT-TEST Hybrid                                 |     |

| 4.10 | ATPG    | for Non-Stuck-At Faults                         |     |

|      | 4.10.1  | Designing an ATPG That Captures Delay Defects   | 231 |

|      |         | 4.10.1.1 Classification of Path-Delay Faults    |     |

|      |         | 4.10.1.2 ATPG for Path-Delay Faults             | 236 |

|      | 4.10.2  | ATPG for Transition Faults                      | 238 |

|      | 4.10.3  | Transition ATPG Using Stuck-At ATPG             | 240 |

|      | 4.10.4  | Transition ATPG Using Stuck-At Vectors          | 240 |

|      |         | 4.10.4.1 Transition Test Chains via Weighted    |     |

|      |         | Transition Graph                                | 241 |

|      | 4.10.5  | Bridging Fault ATPG                             | 244 |

| 4.11 | Other ' | Topics in Test Generation                       |     |

|      | 4.11.1  | Test Set Compaction                             |     |

|      | 4.11.2  | <i>N</i> -Detect ATPG                           |     |

|      | 4.11.3  | ATPG for Acyclic Sequential Circuits            |     |

|      | 4.11.4  | IDDQ Testing                                    |     |

|      | 4.11.5  | Designing a High-Level ATPG                     |     |

| 4.12 |         | Iding Remarks                                   |     |

| 4.13 |         | ses                                             |     |

|      |         |                                                 |     |

|      |         |                                                 |     |

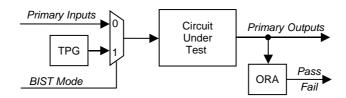

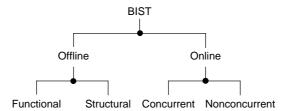

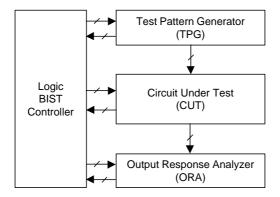

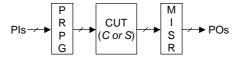

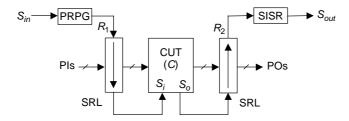

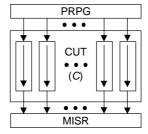

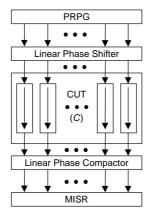

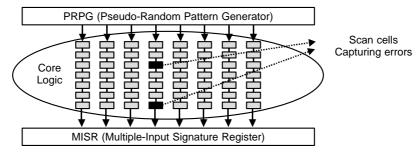

| Log         | gic Bui        | lt-In Seli | f-Test                                       | 263 |

|-------------|----------------|------------|----------------------------------------------|-----|

| Lauı        | ng-Terng       | (LT.) Wa   | ng                                           |     |

| 5.1         | Introd         | luction    |                                              | 264 |

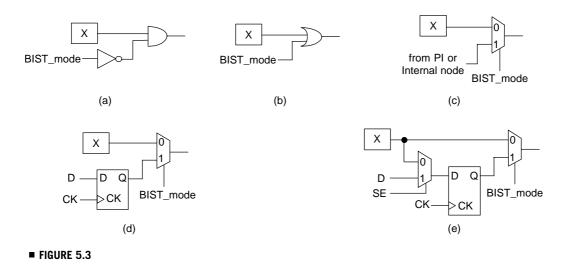

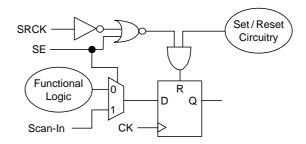

| 5.2         | BIST 1         | Design Rul | es                                           | 266 |

|             | 5.2.1          |            | n Source Blocking                            |     |

|             |                | 5.2.1.1    | Analog Blocks                                |     |

|             |                | 5.2.1.2    | Memories and Non-Scan Storage Elements       |     |

|             |                | 5.2.1.3    | Combinational Feedback Loops                 |     |

|             |                | 5.2.1.4    | Asynchronous Set/Reset Signals               |     |

|             |                | 5.2.1.5    | Tristate Buses                               |     |

|             |                | 5.2.1.6    | False Paths                                  |     |

|             |                | 5.2.1.7    | Critical Paths                               |     |

|             |                | 5.2.1.8    | Multiple-Cycle Paths                         |     |

|             |                | 5.2.1.9    | Floating Ports                               |     |

|             |                | 5.2.1.10   | Bidirectional I/O Ports                      |     |

|             | 5.2.2          | Re-Timii   |                                              |     |

| 5.3         |                |            | eration                                      |     |

| 0.0         | 5.3.1          |            | ive Testing                                  |     |

|             | 3.3.1          | 5.3.1.1    | Binary Counter                               |     |

|             |                | 5.3.1.2    | Complete LFSR                                |     |

|             | 5.3.2          |            | Random Testing                               |     |

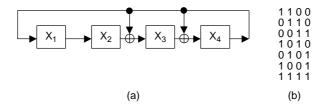

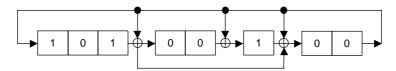

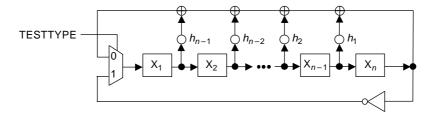

|             | 3.3.2          | 5.3.2.1    | Maximum-Length LFSR                          |     |

|             |                | 5.3.2.2    | Weighted LFSR                                |     |

|             |                | 5.3.2.3    | Cellular Automata                            |     |

|             | 5.3.3          |            | Exhaustive Testing                           |     |

|             | 3.3.3          | 5.3.3.1    | Verification Testing                         |     |

|             |                | 5.3.3.2    | Segmentation Testing                         |     |

|             | 5.3.4          |            | ult Testing                                  |     |

|             | 5.3.5          |            | y                                            |     |

| 5.4         |                |            | e Analysis                                   |     |

| J. <b>T</b> | 5.4.1          | -          | unt Testing                                  |     |

|             | 5.4.2          |            | on Count Testing                             |     |

|             | 5.4.3          |            | e Analysis                                   |     |

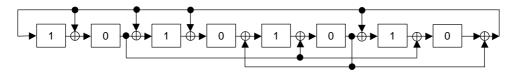

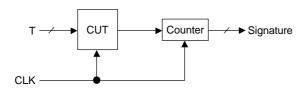

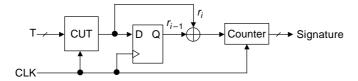

|             | J. <b>T.</b> J | 5.4.3.1    | Serial Signature Analysis                    |     |

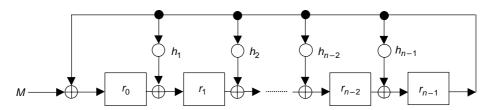

|             |                | 5.4.3.2    | Parallel Signature Analysis                  |     |

| 5.5         | Logic          |            | itectures                                    |     |

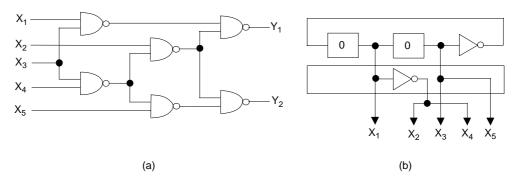

| 5.5         | 5.5.1          |            | chitectures for Circuits without Scan Chains |     |

|             | 3.3.1          | 5.5.1.1    | A Centralized and Separate Board-Level       | 290 |

|             |                | 3.3.1.1    | BIST Architecture                            | 206 |

|             |                | 5.5.1.2    | Built-In Evaluation and Self-Test (BEST)     |     |

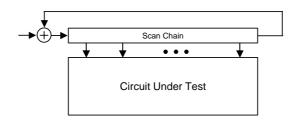

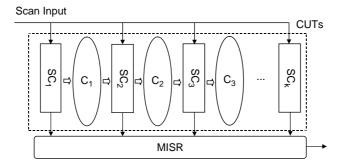

|             | 5.5.2          |            | chitectures for Circuits with Scan Chains    |     |

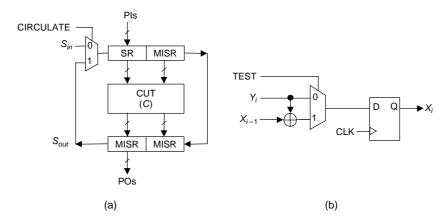

|             | 3.3.2          | 5.5.2.1    | LSSD On-Chip Self-Test                       |     |

|             |                | 5.5.2.1    | Self-Testing Using MISR and Parallel SRSG .  |     |

|             | 552            |            | chitectures Using Register Reconfiguration   |     |

|             | 5.5.3          |            |                                              |     |

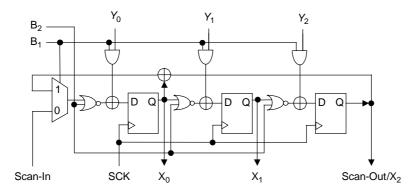

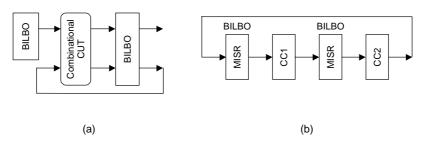

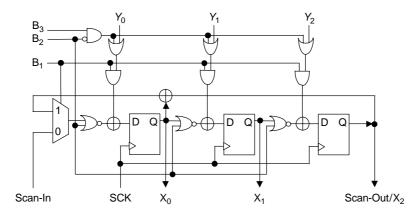

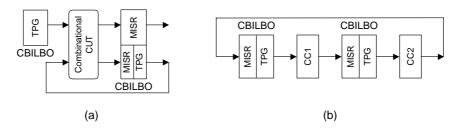

|             |                | 5.5.3.1    | Built-In Logic Block Observer                | 299 |

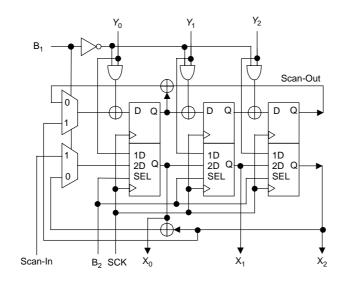

|      |         | 5.5.3.2    | Modified Built-In Logic Block Observer        |       |

|------|---------|------------|-----------------------------------------------|-------|

|      |         | 5.5.3.3    | Concurrent Built-In Logic Block Observer      |       |

|      |         | 5.5.3.4    | Circular Self-Test Path (CSTP)                | . 302 |

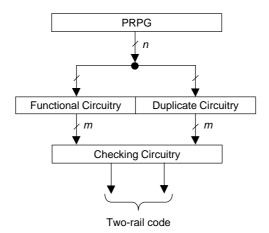

|      | 5.5.4   |            | hitectures Using Concurrent Checking          |       |

|      |         |            |                                               |       |

|      |         | 5.5.4.1    | Concurrent Self-Verification                  |       |

|      | 5.5.5   | Summar     | y                                             | . 304 |

| 5.6  | Fault C |            | nhancement                                    |       |

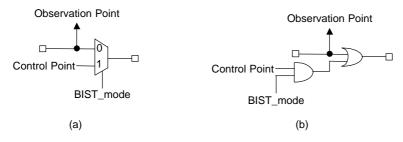

|      | 5.6.1   | Test Poin  | t Insertion                                   | . 305 |

|      |         | 5.6.1.1    | Test Point Placement                          | . 306 |

|      |         | 5.6.1.2    | Control Point Activation                      | . 307 |

|      | 5.6.2   | Mixed-M    | ode BIST                                      | . 308 |

|      |         | 5.6.2.1    | ROM Compression                               | . 308 |

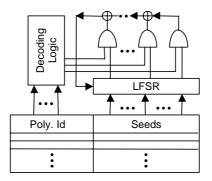

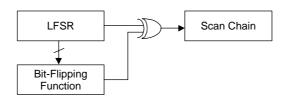

|      |         | 5.6.2.2    | LFSR Reseeding                                | . 308 |

|      |         | 5.6.2.3    | Embedding Deterministic Patterns              |       |

|      | 5.6.3   | Hybrid B   | IST                                           | . 309 |

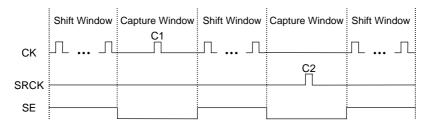

| 5.7  | BIST T  | iming Cor  | itrol                                         | . 310 |

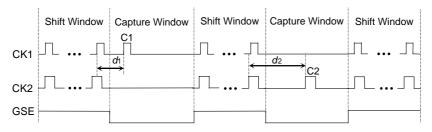

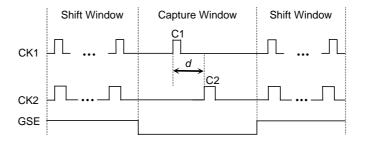

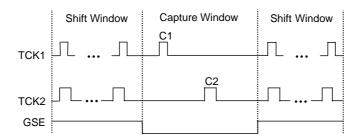

|      | 5.7.1   | Single-Ca  | npture                                        | . 310 |

|      |         | 5.7.1.1    | One-Hot Single-Capture                        | . 310 |

|      |         | 5.7.1.2    | Staggered Single-Capture                      | . 311 |

|      | 5.7.2   | Skewed-I   | Load                                          |       |

|      |         | 5.7.2.1    | One-Hot Skewed-Load                           | . 312 |

|      |         | 5.7.2.2    | Aligned Skewed-Load                           | . 312 |

|      |         | 5.7.2.3    | Staggered Skewed-Load                         |       |

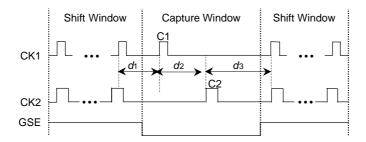

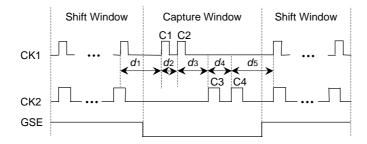

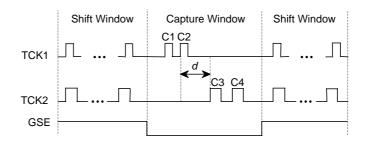

|      | 5.7.3   | Double-C   | Capture                                       |       |

|      |         | 5.7.3.1    | One-Hot Double-Capture                        |       |

|      |         | 5.7.3.2    | Aligned Double-Capture                        |       |

|      |         | 5.7.3.3    | Staggered Double-Capture                      |       |

|      | 5.7.4   | Fault Det  | ection                                        |       |

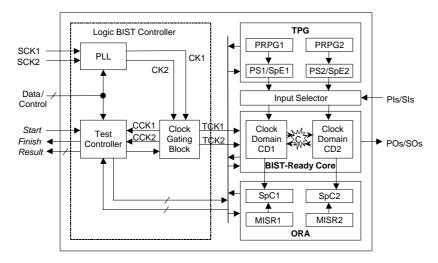

| 5.8  | A Desig | n Practice |                                               | . 319 |

|      | 5.8.1   |            | e Checking and Violation Repair               |       |

|      | 5.8.2   |            | ST System Design                              |       |

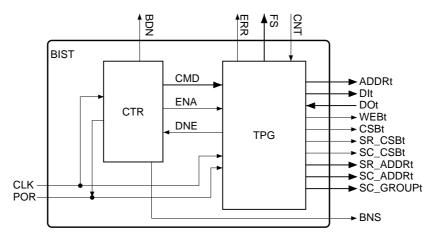

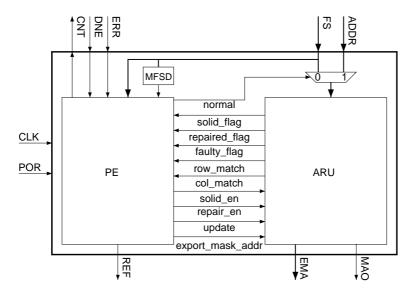

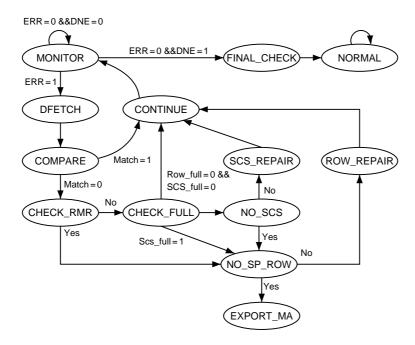

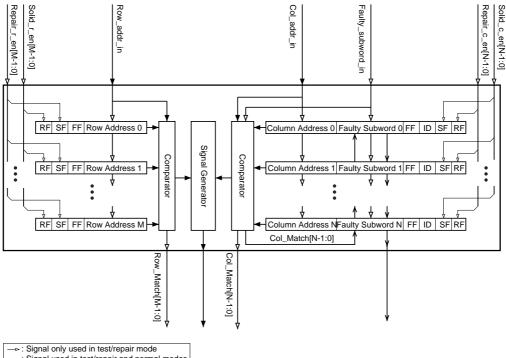

|      |         | 5.8.2.1    | Logic BIST Architecture                       |       |

|      |         | 5.8.2.2    | TPG and ORA                                   |       |

|      |         | 5.8.2.3    | Test Controller                               |       |

|      |         | 5.8.2.4    | Clock Gating Block                            |       |

|      |         | 5.8.2.5    | Re-Timing Logic                               |       |

|      |         | 5.8.2.6    | Fault Coverage Enhancing Logic and Diagnostic |       |

|      |         |            | Logic                                         | . 325 |

|      | 5.8.3   | RTL BIS    | Γ Synthesis                                   |       |

|      | 5.8.4   |            | erification and Fault Coverage                |       |

|      |         |            | ment                                          | . 326 |

| 5.9  | Conclue |            | arks                                          |       |

| 5.10 |         | _          |                                               |       |

|      |         |            |                                               |       |

|      |         |            |                                               |       |

|      |         |            |                                               |       |

Contents

xiii

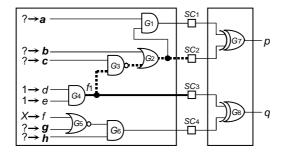

| Tes  | st Com    | pression   | 1                                   | 341 |

|------|-----------|------------|-------------------------------------|-----|

| Xiac | wei Li, K | Luen-Jong  | Lee, and Nur A. Touba               |     |

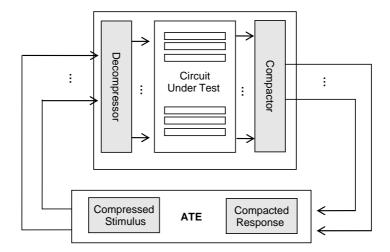

| 6.1  | Introd    | uction .   |                                     | 342 |

| 6.2  |           |            | ompression                          |     |

|      | 6.2.1     |            | ased Schemes                        |     |

|      |           | 6.2.1.1    | Dictionary Code (Fixed-to-Fixed)    |     |

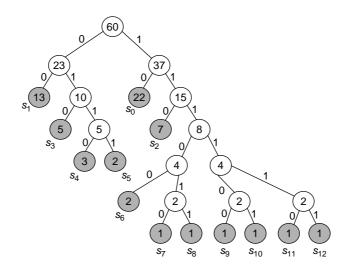

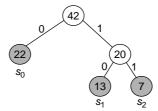

|      |           | 6.2.1.2    | Huffman Code (Fixed-to-Variable)    |     |

|      |           | 6.2.1.3    | Run-Length Code (Variable-to-Fixed) |     |

|      |           | 6.2.1.4    | Golomb Code (Variable-to-Variable)  |     |

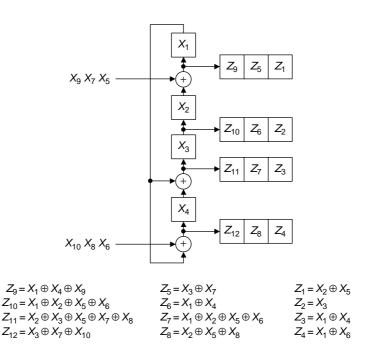

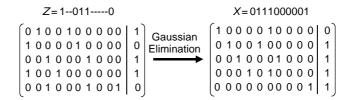

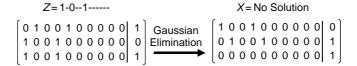

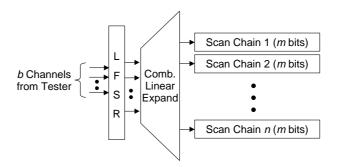

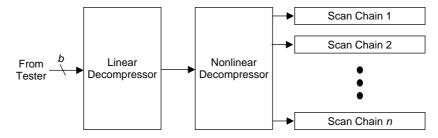

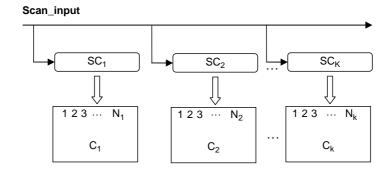

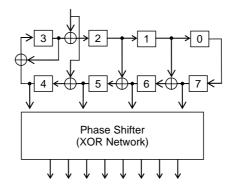

|      | 6.2.2     | Linear-I   | Decompression-Based Schemes         |     |

|      |           | 6.2.2.1    | Combinational Linear Decompressors  |     |

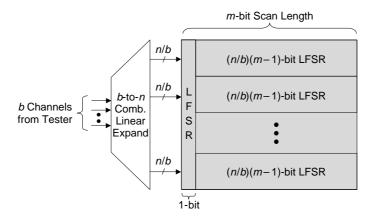

|      |           | 6.2.2.2    | Fixed-Length Sequential             |     |

|      |           |            | Linear Decompressors                | 355 |

|      |           | 6.2.2.3    | Variable-Length Sequential          |     |

|      |           |            | Linear Decompressors                | 356 |

|      |           | 6.2.2.4    | Combined Linear and                 |     |

|      |           |            | Nonlinear Decompressors             | 357 |

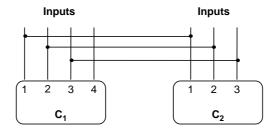

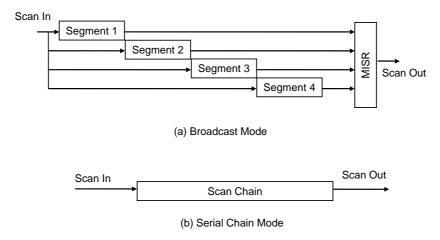

|      | 6.2.3     | Broadca    | ast-Scan-Based Schemes              |     |

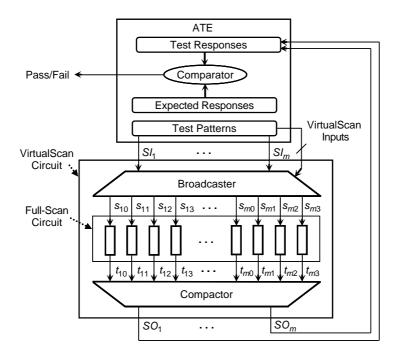

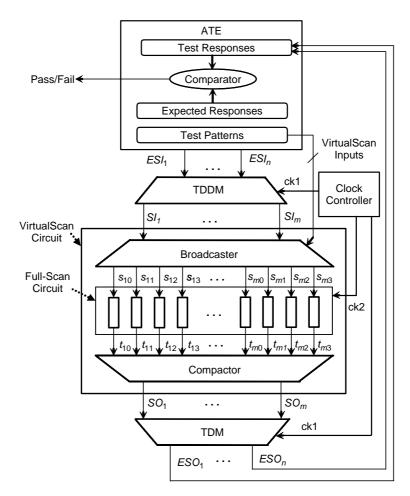

|      |           | 6.2.3.1    | Broadcast Scan                      | 359 |

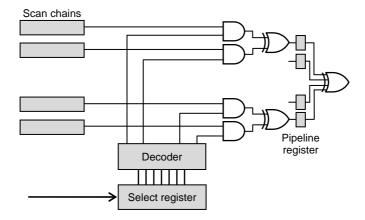

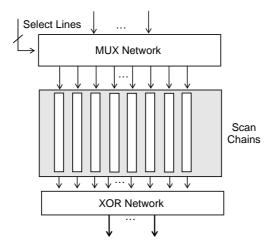

|      |           | 6.2.3.2    | Illinois Scan                       | 360 |

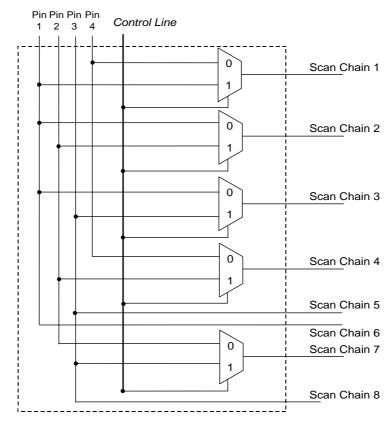

|      |           | 6.2.3.3    | Multiple-Input Broadcast Scan       | 362 |

|      |           | 6.2.3.4    | Reconfigurable Broadcast Scan       |     |

|      |           | 6.2.3.5    | Virtual Scan                        | 363 |

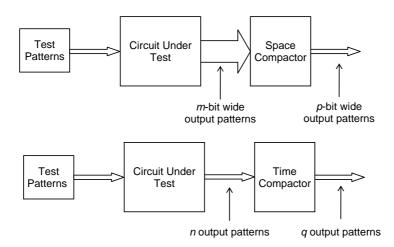

| 6.3  | Test R    | esponse C  | Compaction                          | 364 |

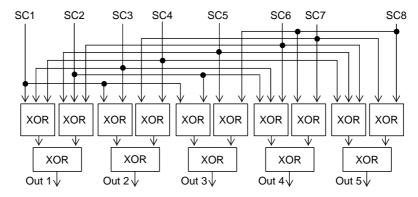

|      | 6.3.1     | Space C    | Compaction                          | 367 |

|      |           | 6.3.1.1    | Zero-Aliasing Linear Compaction     | 367 |

|      |           | 6.3.1.2    | X-Compact                           | 369 |

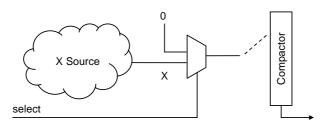

|      |           | 6.3.1.3    | X-Blocking                          |     |

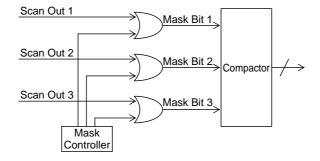

|      |           | 6.3.1.4    | X-Masking                           | 372 |

|      |           | 6.3.1.5    | X-Impact                            | 373 |

|      | 6.3.2     | Time Co    | ompaction                           | 374 |

|      | 6.3.3     | Mixed T    | Time and Space Compaction           | 375 |

| 6.4  | Indust    | ry Practic | es                                  | 376 |

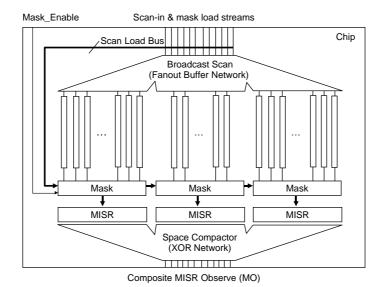

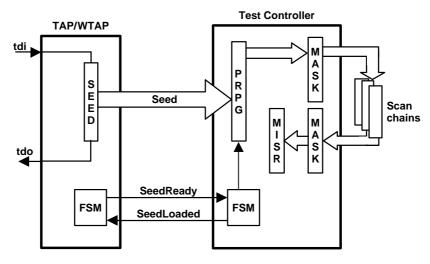

|      | 6.4.1     | OPMISI     | R+                                  | 377 |

|      | 6.4.2     | Embedo     | led Deterministic Test              | 379 |

|      | 6.4.3     | VirtualS   | Scan and UltraScan                  | 382 |

|      | 6.4.4     | Adaptiv    | e Scan                              | 385 |

|      | 6.4.5     | ETCom      | pression                            | 386 |

|      | 6.4.6     | Summa      | ry                                  | 388 |

| 6.5  |           |            | narks                               |     |

| 6.6  |           |            |                                     |     |

| Ackr | nowledgr  | ments      |                                     |     |

| Refe | rences    |            |                                     | 391 |

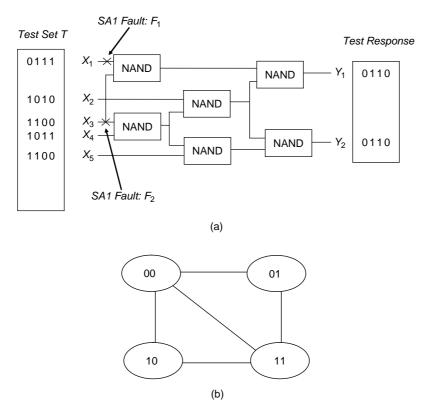

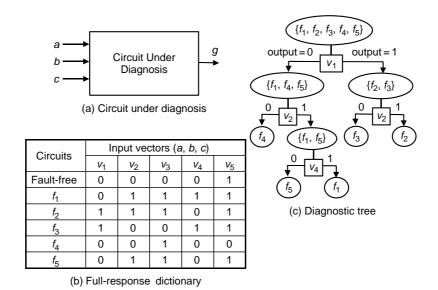

| 7.1 Introduction 7.2 Combinational Logic Diagnosis 7.2.1 Cause–Effect Analysis 7.2.1.1 Compaction and Compression of Fault Dictionary 7.2.2 Effect–Cause Analysis 7.2.2.1 Structural Pruning 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods 7.4.3 Masking-Based Methods |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.2 Combinational Logic Diagnosis 7.2.1 Cause–Effect Analysis 7.2.1.1 Compaction and Compression of Fault Dictionary 7.2.2 Effect–Cause Analysis 7.2.2.1 Structural Pruning 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3 Chip-Level Strategy 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                             |     |

| 7.2 Combinational Logic Diagnosis 7.2.1 Cause–Effect Analysis 7.2.1.1 Compaction and Compression of Fault Dictionary 7.2.2 Effect–Cause Analysis 7.2.2.1 Structural Pruning 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3 Chip-Level Strategy 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                             | 397 |

| 7.2.1 Cause–Effect Analysis 7.2.1.1 Compaction and Compression of Fault Dictionary 7.2.2 Effect–Cause Analysis 7.2.2.1 Structural Pruning 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                         |     |

| 7.2.1.1 Compaction and Compression of Fault Dictionary 7.2.2 Effect-Cause Analysis 7.2.2.1 Structural Pruning 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                            |     |

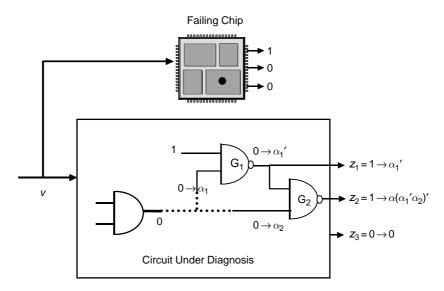

| 7.2.2 Effect-Cause Analysis 7.2.2.1 Structural Pruning 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3 Chip-Level Strategy 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                         |     |

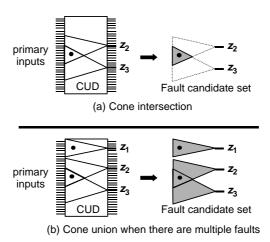

| 7.2.2.1 Structural Pruning 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3 Chip-Level Strategy 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                              |     |

| 7.2.2.2 Backtrace Algorithm 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3 Chip-Level Strategy 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                |     |

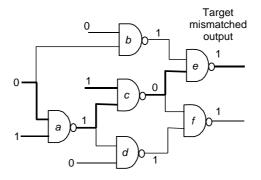

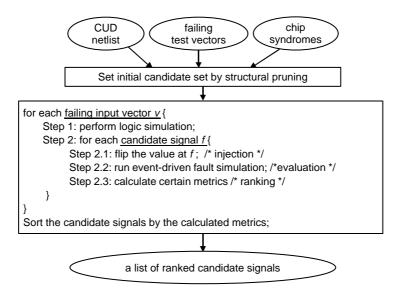

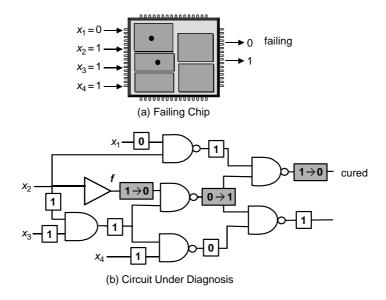

| 7.2.2.3 Inject-and-Evaluate Paradigm 7.2.3 Chip-Level Strategy 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                     |     |

| 7.2.3 Chip-Level Strategy 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                 |     |

| 7.2.3.1 Direct Partitioning 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                           |     |

| 7.2.3.2 Two-Phase Strategy 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                       |     |

| 7.2.3.3 Overall Chip-Level Diagnostic Flow 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                  |     |

| 7.2.4 Diagnostic Test Pattern Generation 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 7.2.5 Summary of Combinational Logic Diagnosis 7.3 Scan Chain Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.3 Scan Chain Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

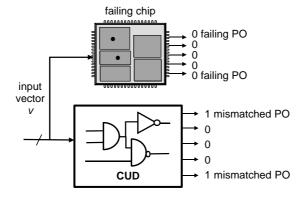

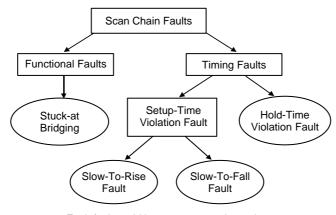

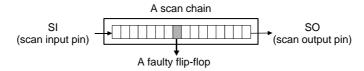

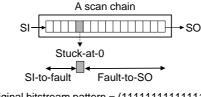

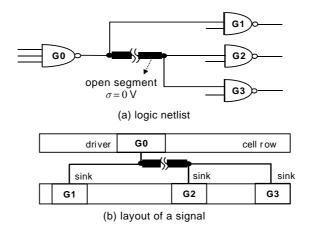

| 7.3.1 Preliminaries for Scan Chain Diagnosis 7.3.2 Hardware-Assisted Method 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 7.3.3 Modified Inject-and-Evaluate Paradigm 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

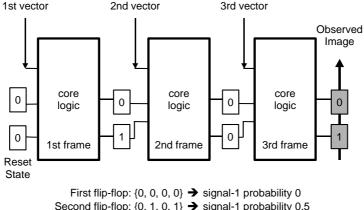

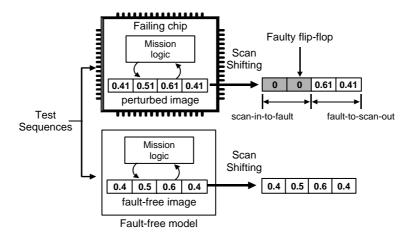

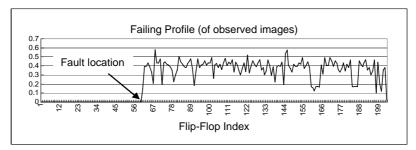

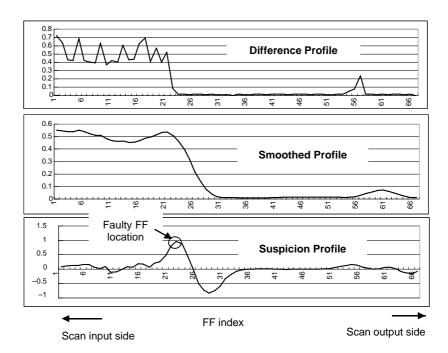

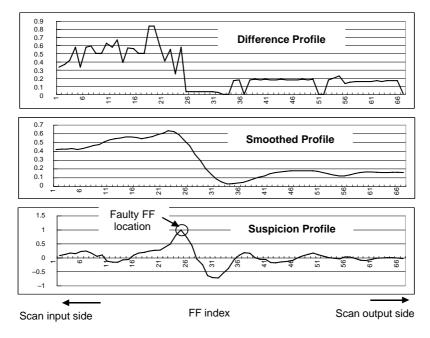

| 7.3.4 Signal-Profiling-Based Method 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 430 |

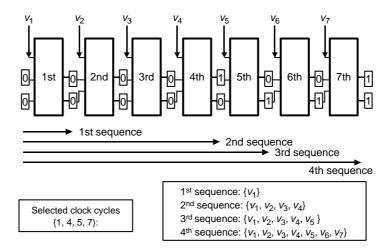

| 7.3.4.1 Diagnostic Test Sequence Selection 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 432 |

| 7.3.4.2 Run-and-Scan Test Application 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 434 |

| 7.3.4.3 Why Functional Sequence? 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 434 |

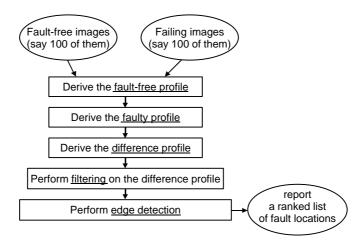

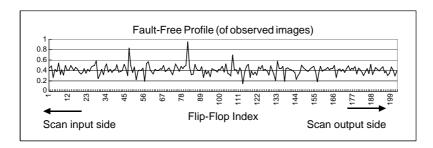

| 7.3.4.4 Profiling-Based Analysis 7.3.5 Summary of Scan Chain Diagnosis 7.4 Logic BIST Diagnosis 7.4.1 Overview of Logic BIST Diagnosis 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 434 |

| 7.3.5 Summary of Scan Chain Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 435 |

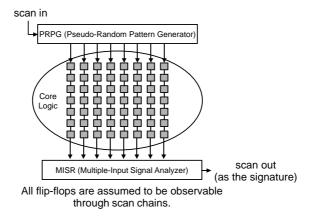

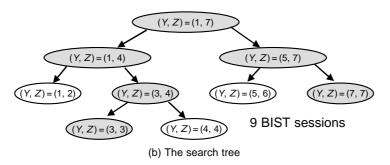

| 7.4 Logic BIST Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 7.4.1 Overview of Logic BIST Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 441 |

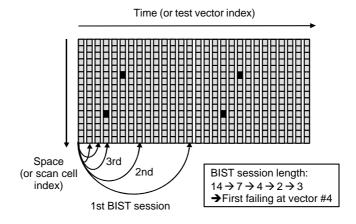

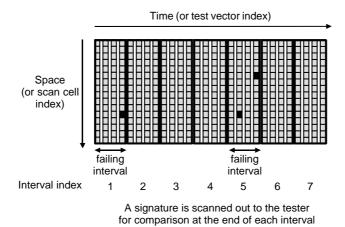

| 7.4.2 Interval-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 442 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

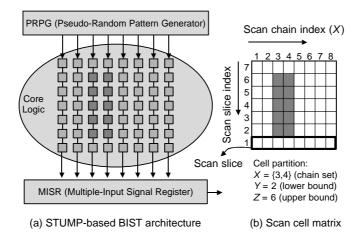

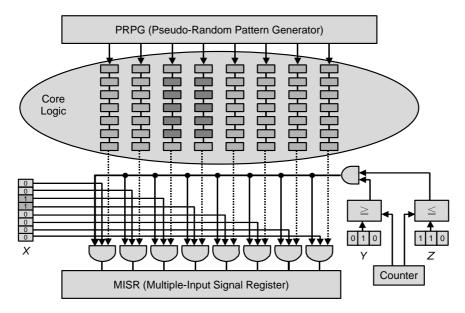

| 7.4.3 Masking-Based Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 443 |