[Home](index.html) | [Quartus](quartus.htm) | [Blink](blink.htm) | Simulacija

# Simulator ModelSim

**ModelSim** je program za simulacijo digitalnega vezja opisanega v jeziku VHDL ali Verilog.

Program *Modelsim - Intel FPGA Starter Edition* je brezplačno dostopen na [www.altera.com](www.altera.com)

v okviru programskega paketa [Quartus Prime](https://www.altera.com/products/design-software/fpga-design/quartus-prime/download.html).

Simulacijo lahko poženemo iz orodja **Quartus**, ki pripravi projekt s skripto za prevajanje, ali

pa samostojno, tako da naredimo nov projekt programa **ModelSim**.

## Samostojen ModelSim projekt

**ModelSim** poženemo tako, da v Windows Start poiščemo ModelSim Intel FPGA Starter Edition.

Program odpre okno v katerem kliknemo **Jumpstart** in nato Create Project.

Določimo ime in lokacijo projekta, v naslednjem oknu **Add items to the Poject**

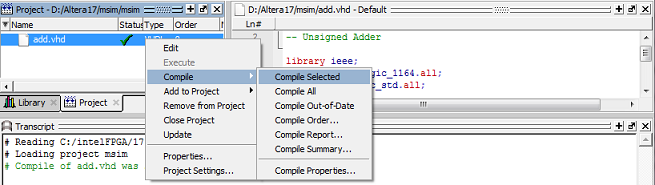

pa dodamo v projekt VHDL/Verilog datoteke. Datoteke najprej prevedemo z desnim klikom na ime datoteke

v oknu **Project** in izbiro Compile > Compile Selected ali Compile All.

V primeru napak, se v oknu **Transcipt** izpiše sporočilo o neuspešnem prevajanju, z dvoklikom na

rdeče obarvano besedilo pa se odpre okno s podrobnejšim opisom napake. Kodo popravimo v urejevalniku,

ki ga odpremo z dvoklikom na ime vezja v oknu **Project**.

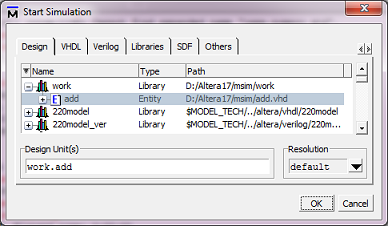

Simulacijo pričnemo s Simulate > Start Simulation..., ki odpre okno v katerem s klikom odpremo

knjižnico work, izberemo opis vezja (Design Unit(s)) in potrdimo z OK.

## Potek simulacije

Rezultate simulacije običajno opazujemo v obliki poteka signalov v oknu **Wave**, ki jih moramo v okno

najprej dodati. Če simuliramo le enoto (manjše vezje brez testne strukture) dodamo kar vse signale:

Add > To Wave > All items in region.

Kadar imamo več enot in signalov, pa jih izbiramo: v levem oknu **Instance** s klikom izberemo

ustrezno enoto, da se pokažejo signali te enote v sosednjem oknu **Objects**, od koder jih z miško

prenesemo v **Wave**.

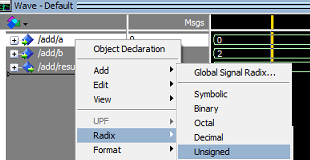

Vrednosti večbitnih signalov so privzeto prikazane v dvojiški obliki, lahko pa format prikaza nastavimo

z desnim klikom na enega ali več izbranih signalov in izbiro v meniju Radix. Najbolj uporabni številski

formati so Decimal (predznačeni desetiški), Unsiged (nepredznačeni desetiški) in šestnajstiški.

Če nimamo testne strukture, moramo v simulatorju nastaviti vrednosti vhodnih signalov, kar storimo

z ukazi grafičnega vmesnika (GUI) ali pa z ukazi, ki jih vnašamo v konzolo. Ta način je uporaben le za

zelo majhna in enostavna vezja, sicer pa je najbolje da dodamo v projekt testno strukturo, ki naredimo

npr. s spletnim orodjem [Grafični Test Bench](https://lniv.fe.uni-lj.si/graftb/). V tem primeru izberemo

entiteto testne strukture ob zagonu simulacije.

### Nastavitev vhodov z GUI

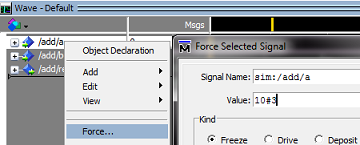

V oknu **Wave** z desnim klikom na signal izberemo Force... in pod Value nastavimo vrednost.

Vrednost vnesemo v vektorski (binarni) obliki, ali pa kot desetiško

vrednost s predpono 10#, npr. desetiško število 3 zapišemo kot 10#3.

Periodične signale, npr. uro, nastavimo tako, da namesto Force... izberemo Clock... in določimo

ustrezno periodo (Period). Ko nastavimo vhode, izvedemo simulacijo za določen čas (100 ps) s tipko **F9**,

nato spremenimo enega ali več vhodov in ponovno izvedemo simulacijo. Ob pregledu rezultatov lahko

spreminjamo skalo - Zoom s tipkami (**I** = Zoom In, **O** = Zoom Out, **F** = Zoom Full) in številski format.

Ta način izvedbe simulacije je precej zamuden, zato raje uporabljamo nastavitev vhodov z ukazi ali

pa s testno strkuturo.

### Nastavitev vhodov z ukazi

Ukaze pišemo v spodnje okno **Transcript**.

Ukaz ```force``` uporabimo za nastavitev signalov v simulatorju, kadar niso nastavljeni s

testno strukturo. Med simulacijo lahko nastavimo vrednost kateregakoli signala, vendar je

smiselno nastavljati le signale, ki so **vhodi** vezja.

Primer: dve obliki ukaza, ki nastavi signal a vezja add na vrednost 3:

```tcl

force /add/a 0011

force a 10#3

```

V prvem primeru smo natančno zapisali pot do signala v obliki /ime_vezja/ime_signala in vrednost

v privzeti vektorski obliki. Zapis poti do signala nam omogoča, da nastavimo signal v poljubni

hierarhični komponenti vezja. Kadar simuliramo le eno vezje, lahko pot izpustimo in zapišemo samo

ime signala. Če želimo zapisati vrednost v desetiškem zapisu uporabimo predpono 10#, negativno desetiško vrednost pa določimo tako:

```tcl

force a -10#3

```

V splošnem lahko določimo več vrednosti, ki naj jih dobi signal v nekem časovnem zaporedju:

```TCL

force a 10#0, 10#4 @100 ps, 10#5 @200 ps

force a 10#0, 10#4 100 ps, 10#5 200 ps

```

Prvi ukaz nastavi signal a najprej na 0, potem na 4 ob času 100 ps in nato na 5 ob času 200 ps.

S simbolom @ označujemo absolutni simulacijski čas, če ga izpustimo pa časovni parameter predstavlja

relativni čas (drugi primer).

S stikalom -r določimo, da naj se časovno zaporedje ponavlja z določeno periodo.

Uro bi naprimer določili takole:

```TCL

force clk 1 0 ps, 0 {100 ps} -r 200 ps

```

Simulacijo poženemo za določen čas z ukazom run:

```TCL

run 500 ps

```

**Privzete vrednosti**

Privzeti format zapisa vrednosti ali privzeto časovno enoto lahko spremenimo in v tem primeru

ni potrebno zapisati predpone oz. časovne enote. Spodnja dva ukaza nastavita časovno enoto ns in

privzeti številski format unsigned:

```tcl

set UserTimeUnit ns

set DefaultRadix unsigned

```

## Simulacija iz programa Quartus

Simulacijo izvedemo s Tools > Run Simulation > RTL Simulation. Če se simulator ne odpre, preverimo ali

smo namestili ModelSim in nastavili pot do programa: Tools > Options, EDA Tool Options: ModelSim-Altera: `C:\intelFPGA_lite\17.0\modelsim_ase\win32aloem`

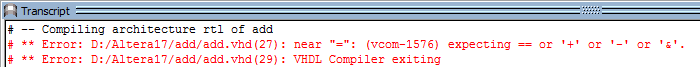

Ko se program **ModelSim** odpre, najprej izvede skripto za prevajanje datotek in javi morebitne napake.

Če bi npr. namesto prireditvenega operatorja <= uporabili le =, bi program v oknu **Transcript** izpisal

sporočilo o napaki, ki vsebuje ime datoteke, vrstico v oklepaju in vrsto napake.

Napako v urejevalniku (npr. v programu **Quartus**) popravimo, shranimo in ponovno poženemo simulator.

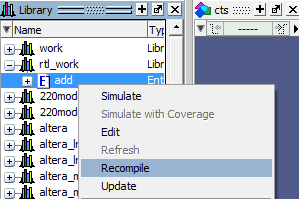

To lahko storimo s skripto v oknu **Transcipt**, ki jo s puščico navzgor prikličemo iz zgodovine,

npr. `do projekt_run_msim_rtl_vhdl.do`, ali pa tako da v oknu **Library** odpremo knjižnico rtl_work,

desni klik na add in izberemo Recompile. Simulacijo pričnemo s klikom na Simulate.