[Home](index.html) | Quartus | [Simulacija](modelsim.htm) | [Komponente IP](quartus-ip.htm)

# Osnove programa Quartus Prime

Predstavili bomo najbolj osnovne korake idelave RTL projekta v programu Intel Quartus Prime 2017.

V mapi projekta so poleg izvorne kode (.vhd) še vsaj tri ključne datoteke:

* projekt.qpf, glavna datoteka z opisom projekta,

* projekt.qsf, nastavitve FPGA, definicije priključkov, vključene datoteke...

* de0.sdc, uporabniške nastavitve: parametri ure

## Nov projekt

Prikazali bomo uporabo orodja Quartus na primeru projekta z opisom seštevalnika.

Projekt za FPGA na razvojni plošči je najbolje začeti s predlogo, kjer so definirani parametri

vezja in omejitve. Na lokalnem disku naredi novo mapo (npr. c:\projekt\add) in kopiraj v mapo

datoteke iz predloge projekta za razvojno ploščo DE0 Nano: [DE0_projekt.zip](DE0_projekt.zip).

Z dvoklikom na **projekt.qpf** odpri program Quartus.

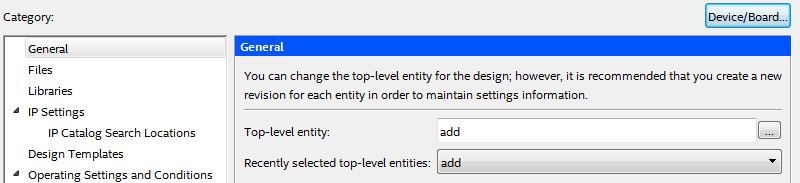

Najprej nastavi ime glavne entitete: odpri Assignments > Settings, poišči General

in v Top-level entity vnesi `add`.

Nato klikni New in izberi VHDL file, tako da se odpre urejevalnik, kamor vnesi opis vezja.

Za začetek si bomo pomagali s čarovnikom Edit > Insert Template. Odpri VHDL > Full Designs > Arithmetic > Adders > Unsigned Adder in klikni gumb **Insert** in zapri okno. V urejevalniku spremeni ime vezja iz

unsigned_adder v add in shrani datoteko kot add.vhd.

```vhdl

-- Quartus Prime VHDL Template

-- Unsigned Adder

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity add is

generic

(

DATA_WIDTH : natural := 8

);

port

(

a : in unsigned ((DATA_WIDTH-1) downto 0);

b : in unsigned ((DATA_WIDTH-1) downto 0);

result : out unsigned ((DATA_WIDTH-1) downto 0)

);

end entity;

architecture rtl of add is

begin

result <= a + b;

end rtl;

```

Start Analysis and Synthesis (ctrl+k)

Run Simulation > RTL

## Analiza in sinteza vezja

Prevajanje vezija je zahteven proces in traja dolgo, zato je smiselna izvedba prevajanja po korakih

in preverjanje delovanja s [simulacijo](modelsim.htm). Cilj prevajanja je prevorba datotek z opisom vezja (*.vhd) v

datoteke za nastavitev programirljivega vezja (*.sof, SRAM Object File). Potek prevajanja je sestavljen iz:

* Analysis & Synthesis, analiza opisa vezja, sinteza gradnikov RTL, optimizacija in tehnološka preslikava

* Fitter, preslikava gradnikov v elemente vezja FPGA in povezovanje

* Assembler, izdelava datoteke za programiranje

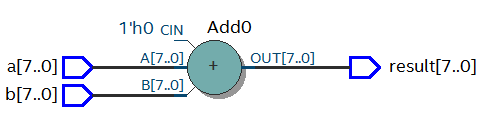

Kadar želimo le preveriti ali je opis vezja brez napak in primeren za sintezo, izberemo korak prevajanja:

Start Analysis & Elaboration. Program javi morebitne napake v oknu Messages (okno odpremo in zapremo z

**alt+3**). Po tem koraku lahko pregledamo gradnike na nivoju RTL iz katerih bo sestavljeno vezje:

Tools > Netlist Viewers > RTL Viewer.

Celotno prevajanje izvedemo s Processing > Start Compilation.